千兆位级串行I/O技术有着极其出色的优越性能,但这些优越的性能是需要条件来保证的,即的信号完整性。例如,有个供应商说,他们次试图将高速、千兆位级串行设计用于某种特定应用时,失败率为90%。为了提高成功率,我们可能需要进行模拟仿真,并采用更复杂的新型旁路电路。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA采用了逻辑单元阵列LCA这样一个概念,内部包括可配置逻辑模块CLB、输出输入模块IO和内部连线三个部分。 现场可编程门阵列(FPGA)是可编程器件。与传统逻辑电路和门阵列相比,FPGA具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及个模块之间或模块与I/O间的连接方式,并终决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并终决定了FPGA所能实现的功能, FPGA允许无限次的编程。

Spartan-6 FPGA的GTP工作性能取决于PCB的信号完整性,PCB设计过程中需要考虑到以下因素:板的叠层结构,元器件的布局,信号走线。

电源与叠层

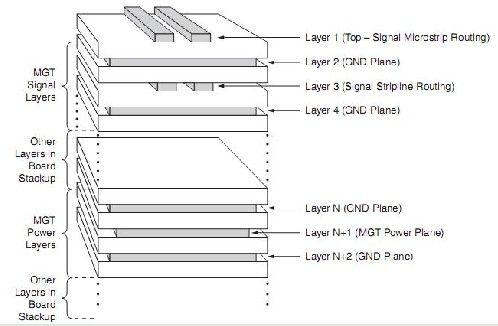

针对Spartan-6 FPGA的GTP transceiver,叠层可以分为两组,电源分布层和信号走线层。电源层用来连接GTP的MGTACC,MGTAVCCPLL,MGTAVTTTX和MGTAVTTRX电源引脚。叠层结构可以参考下图。

在上图的叠层中,地平面层位传输信号线提供了信号回流路径。同时,由于在两信号层中间有屏蔽的平面,在信号走线时就可以不考虑相邻层走线的所需考虑的问题,并且提供了更多的信号路径。

GTP的电源层应该与地平面紧密相邻,增加耦合效果,地平面可以为GTP的电源平面提供屏蔽,屏蔽电源平面来自上一层或下一层信号引起的噪声干扰。

实际上,从另一个角度考虑,即当电源的噪声出现在高频范围,随着频率增大,越来越难找到电容可以覆盖此频率范围。随着电容值的减小,相关的杂散电感和封装的电阻值并不相应改变,所以频率响应也不会发生太大变化。

GTP的电源管脚和电源分布网络之间的连接对GTP的工作性能起着很关键的作用。PDN,和FPGA需要低阻抗和低噪声的连接。FPGA的GTP电源容忍噪声为10mVpp,在10KHz到80MHz的范围内,电源可以用一个小块平面。

电容摆放

旁路电容除了考虑容值大小外,需要考虑的另一重要方面是电容的放置。

一般的规则是,电容值越大则其放置要求越不严格。若电容值较小,则电容应该尽可能靠近电源和地的引脚。

GTP的电源分割区域的位置和GTP滤波电容的位置也可以参考下图。

信号走线

应该避免GTP信号走线和SelectIO信号走线在相邻层,其各自的回流路径也应保持分离,包括过孔。

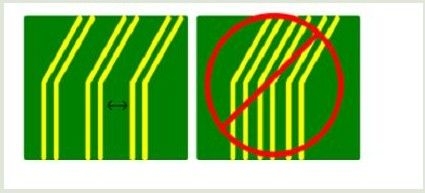

差分线路对之间以及差分线路和其他线路之间都要保持一定的距离,这一点是很重要的。下图所示。

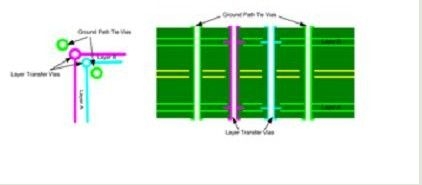

千兆位级信号差分线路应当尽可能避免改变走线层。如果跨层传输是必须的,那么需要特别小心。首先,必须提供一个完整的返回路径。所以我们必须把层A的参考层和层B的参考层耦合在一起。理想的情况是两个参考层都是地层。在这种情况下,返回路径可以通过在转层过孔附近放置另一个连接两个参考层的过孔来实现。下图给出这种技术的示意图。

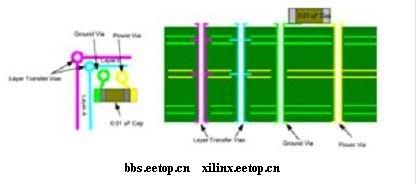

如果参考层是不同的(一个是地层,另一个是电源层),则需要在离过孔尽可能近的地

方放置 0.01μF 的电容来连接两个参考层,降低回流路径的阻抗。如下图所示。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。