二、为仪表放大器、运算放大器和ADC提供基准电压

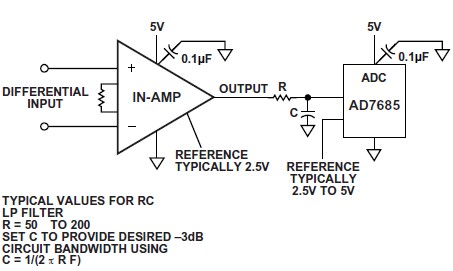

图7所示的是一个单电源电路,是用一个仪表放大器驱动一个单端模数转换器(ADC)。放大器基准电压源提供零差分输入时的偏置电压,而ADC基准电压源则提供比例因子。通常在仪表放大器输出端与ADC输入端之间使用一个简单的RC低通抗混叠滤波器来降低带外噪声。设计师一般倾向于采取简单的办法,比如利用电阻分压,来为仪表放大器和ADC提供基准电压。在某些仪表放大器应用中,这种方法有可能导致误差。

图7 典型单电源电路中仪表放大器驱动ADC

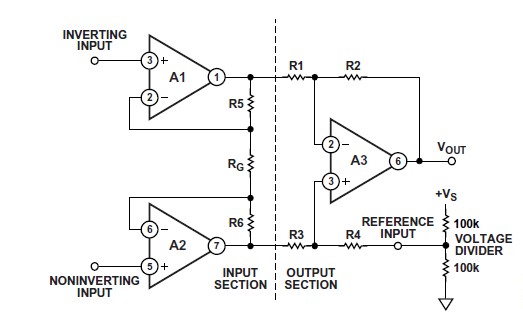

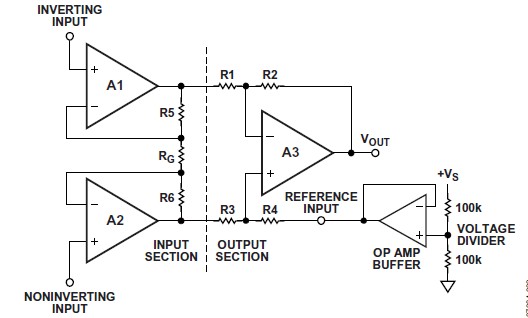

通常认为仪表放大器基准输入端是高阻抗,因为它是一个输入端口。因此,设计师可能将高阻抗源,比如电阻分压器连接至仪表放大器的基准电压引脚。对于某些类型的仪表放大器,这可能导致严重错误(见图8)。

图8 不恰当的使用简单分压器来直接驱动三运放结构仪表放大器的基准引脚

例如,一种流行的仪表放大器设计结构采用三运算放大器,其连接方法如图8所示。总信号增益为:

其中:

若通过低阻抗源驱动,基准输入端的增益为单位增益。但在此例中,仪表放大器的基准引脚直接与一个简单的分压器相连。这破坏了减法电路的对称性以及分压电路的分配比,降低了仪表放大器的共模抑制能力及其增益。但在某些情况下,R4是可调的,因而可降低其电阻值,降低量等于分压电阻的并联值(本例为50k )。此时,电路的表现就像是将相当于电源电压一半的低阻抗电压源连接到保持原始值的R4上。此外,还可使减法器的维持不变。

如果仪表放大器采用单芯片封装(IC),则不能使用这种方法。另一考虑因素是,分压器电阻的温度系数还应能跟踪R4以及减法电路中的其它电阻。,这种方法排除了调节基准电压的可能。另一方面,如果试图通过在分压器中使用小电阻值来降低附加电阻,则会增加电源的耗散电流,进而增加电路功耗。这并非好的设计方法。

图9给出了一种较好的解决方案,该方案在分压器与仪表放大器基准输入端之间采用了一个低功耗运放缓冲器。这种方法消除了阻抗匹配和温度跟踪问题,并且允许轻松调节基准电压。

图9 利用运算放大器的低阻抗输出端驱动仪表放大器的基准引脚

三、在利用电阻分压供电电源给运放提供基准的情况下保持PSR

一个经常被忽视的问题是,电源电压VS的噪声、跳变、或漂移会反馈到基准输入端进而直接叠加到输出上,仅受分压比影响而衰减。实际的解决方案包括采用旁路和滤波器,甚至用高的基准IC,比如ADR121,来产生基准电压,而不是对VS进行分压。

在设计同时采用仪表放大器和运算放大器的电路时,这种考虑非常重要。电源抑制(PSR)技术可将放大器与电源嗡嗡声、噪声以及跳变电压隔离。这一点非常重要,因为许多实际电路都包含、连接至或存在于电源电压不够理想的环境。除此之外,电源线路中存在的交流信号可能流回电路并被放大,在某种条件下,还可能激发寄生振荡。

现代运算放大器和仪表放大器的设计已具有出色的低频电源抑制性能。多数工程师也将此视为必然。许多现代运算放大器和仪表放大器的PSR值达80dB至100dB以上,可使电源变化的影响降低1万至10万倍。即使PSR值仅为40dB,电源变化与放大器间的隔离系数也可达100。然而,高频旁路电容(如图1至图7所示)总是可取的,往往也是必要的选择。此外,当设计师利用简单的电阻分压器来分压供电电源以及运放缓冲器来为仪表放大器提供基准电压时,电源电压的任何变化都会几乎没有衰减的顺利通过电路,直接叠加到仪表放大器的输出电平上。因此,除非采用低通滤波器,否则,IC将失去通常较为出色的PSR性能。

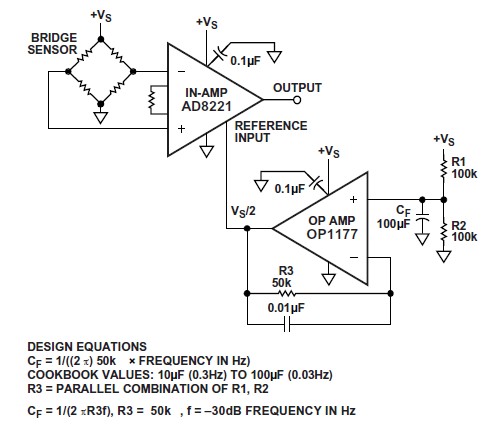

在图10中,一个大电容被加至分压器,以滤除电源变化,从而使PSR保持不变。该滤波器的3dB极点由R1/R2并联组合及电容CF设定。该极点应设为低于所关心的频率10倍左右。

图10 对基准电路进行去耦处理以维持PSR

图10给出了一组3dB极点频率约为0.03Hz的参数。跨接在R3两端的小电容(0.01 F)可使电阻噪声。

滤波器充电需要一定时间。根据图中所示值,基准输入端的上升时间为几个时间常数(其中,T=R3Cf=5s),大约10至15秒左右。

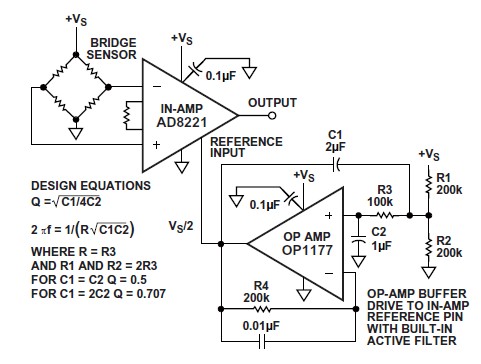

图11所示电路作了进一步改进。这种情况下,运放缓冲器充当一个有源滤波器,可以用较小的电容实现等量的电源去耦。此外,有源滤波器可设计提供更高的Q值,从而获得更快的开启时间。

基于图11所示元件值,对电路进行了测试。其中,电源电压为12V,6V滤波后的基准电压被提供给仪表放大器。一个频率可调的1V峰峰值正弦波被用来调制12V电源,并将仪表放大器增益设为单位增益。在这些条件下,用示波器监测VREF和仪表放大器的输出,随着频率的降低,示波器上未出现交流信号,直到接近8Hz。在连接低电平输入信号到仪表放大器时,测得该电路的电源范围为4V至25V以上。电路开启时间约为2秒。

图11 运放缓冲器接成有源滤波器驱动仪表放大器基准引脚

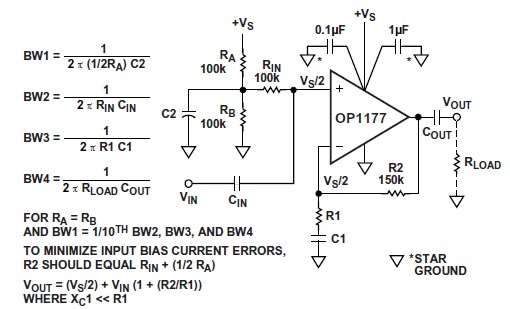

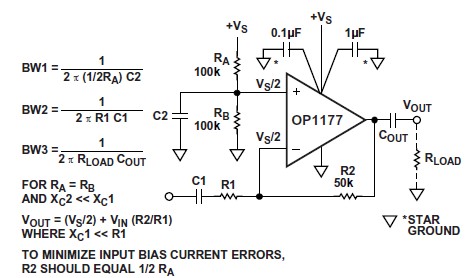

四、对单电源运算放大器电路进行去耦

单电源运算放大器电路要求对输入共模电平进行偏置以处理正负摆动的交流信号。当采用电阻分压供电电源的方法来提供偏置时,必须进行足够的去耦处理,以维持PSR不变。

一种常见的,但是错误的做法是通过一个带有0.1 F旁路电容的100k /100k 分压电路来向运算放大器的同相端提供VS/2偏置。如果使用这些值,电源去耦往往显得不足,因为其极点频率仅为32Hz。

图12 单电源同相放大器电路的正确去耦方法

当电路工作在不稳定的环境下,图12(同相放大)和图13(反相放大)给出了如何获得效果的VS/2去耦偏置电路。两种情况下,偏置功能均由同相输入端提供,反馈使反相输入端获得相同的偏置,而单位直流增益则将输出偏置为同一电压。耦合电容C1与BW3一致,滚降低频增益。

如图12所示,在使用100k /100k 电阻分压电路的时候,一条经验法则是,使用值至少为10 F的C2,实现0.3Hz时有?3dB的滚降特性。实际上,100 F(0.03Hz极点频率)的值就足以应付所有电路了。

图13 单电源反相放大器电路的正确去耦方法

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。