1 引言

为了满足消费类和工业H.264编码器要求,以下就是我们给出的一种支持H.264高清编码器的片上系统MG3500应用设计和相关应用。

2 MG3500 SoC简介

MG3500 SoC其内部集成有嵌入式ARM9处理器、NAND/NOR闪存、SD/SDIO/MMC/CE-ATA接口、10/100/千兆以太网的MAC和USB2.0 OTG端口,以及基于可靠的互联网的AES/SHA加密算法、UART、JTAG、串行控制和通用I/O。240 MHz ARM9处理器包含DSP扩展和各16 KB的指令高速缓存、数据缓存和暂存存储器。

MG3500 SoC支持H.264的基本档次、主要档次和高达4.1级的高画质。在主要档次和高画质中的宏模块自适应场/帧编码允许隔行素材每比特质量。

2.1 MG3500 SoC主要特性

(1)高清H.264编解码器双码流高清/标清H.264编解码器,支持H.264的基本档次、主要档次和高画质,H.264编解码分辨率高达1 920×1 080 i,可编程的分辨率和帧频,多码流标清编解码,视频比特率范围:64 Kb/s~62.5 Mb/s,宏模块自适应场/帧。

(2)MPEG-2解码器 高清/标清解码器实时将高清MPEG-2码流转换为H.264格式,多码流标清MPEG-2解码。

(3)JPEG/MJPEG编解码器JPEG编解码器,高清/标清MJPEG,支持可交换图像文件格式。

(4)音频编解码器 高保真双通道AAC-LC编解码器,MP2格式编解码器,MP1和MP3格式解码器,杜比数码5.1声道解码,G.711编解码器,可调的比特率和采样频率,支持编解码器的扩展,1路SONY/PHILIPS家用数字音频输出接口或2路I2S音频I/O端口。

(5)视频输入处理器 可调的视频直接输入,2个ITU-R BT.1120并行接口,4个ITU.R BT.656并行接口,2个先进的视频输入处理器,支持数字图像稳定功能,支持平滑数码变焦。

(6)视频输出处理器可以支持ITU-R BT.1120或ITU-R BT.656的高清/标清输出,多码流解码支持画中画和多路混合视频输出,18位或8位RGB格式LCD接口,高质量的视频压缩输出,2个带α混合和游标的覆盖图层,生成可选择的外部同步信号。

(7)内置有ARM926-EJ处理器 240 MHz通用处理器,16 KB数据高速缓冲存储器,16 KB的指令高速缓冲存储器,16 KB暂存存储器。

(8)系统连通性 1个10/100/千兆以太网的MAC,1个USB2.0 OTG端口,高速比特流I/O端口,AES/SHA加密。

(9)外围设备接口 支持SD/SDIO/MMC/CE-ATA接口,支持IDE和Compact Flash

(10)通用接口 2个SPI或两总线串行通信接口,3个UART接口,3个脉冲宽度调节器,8路专用GPIO。可扩展到72路GPIO。

(11)系统 内核电压为1.0 V±10%,SDRAM的电压为1.8 V±10%,I/O端口电压为1.8 V,2.5 V,3.3 V±10%,单晶驱动音/视频锁相环。

(12)功耗 H.264高清30fps+AAC编码750 mW。

2.2 MG3500 SoC的接口

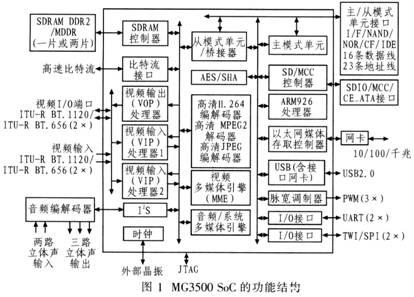

图1是MG3500 SoC的功能结构框图。MG3500 SoC内2个视频输入处理器(VIP)、1个视频输出处理器(VOP)、1个视频多媒体引擎(MME)和1个音频多媒体引擎。

2.2.1 视频接口

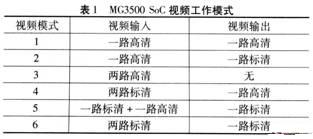

两路8位视频输入接口支持独立的ITU-R BT.656输入,每路视频输入支持独立的时钟和同步信号。支持标清输入,将时钟频率设置100 MHz以上也可支持包括来自高清传感器的8位视频信号在内的非标准视频信号。两路8位的视频输入接口还可组合成一路16位的ITU-R BT 1120高清输入接口。MG3500 SoC支持的工作模式,如表1所列。

2.2.2 音频接口

MG3500 SoC的音频多媒体引擎能使所有的音频编解码器有效。音频接口包括2个I2S输入和3个I2S输出。其中一个I2S输入和音频时钟相连,另一个I2S输入及3个I2S输出与另一个时钟相连。其中一个音频输出口还可用于产生S/PDIF兼容音频。

2.2.3 以太网口、USB接口及SD/MMC接口

MG3500 SoC的以太网媒体存取控制器(MAC)通过一个媒体独立接口(MII)、精简的独立媒体接口(RMII)或吉比特媒体独立接口(GMII)来支持10/100/千兆以太网,MG3500SoC还可以直接接到支持RevMII接口的以太网交换机。USB接口支持高速USB 2.0 OTG,可以做主设备或从设备。SD/MMC接口用来支持SD/SDIO/MMC/CE-ATA设备。这种4位的接口时钟频率可达50 MHz。

2.2.4 HOST接口

MG3500 SoC可工作在主从两种模式下。当MG3500 SoC工作在主模式时,HOST接口的信号线用于连接NOR Flash,NAND Flash,COMPACT Flash,IDE以及他外部设备。串口及其他I/O端口。MG3500 SoC含有用于通信的多个异步收发传输器接端口(UART),用于控制的脉冲宽度调节器(PWM),用于外设控制的两总线串行通信接口(TWI)及串行外设端口(SPI)。MG3500 SoC的8个专用通用I/O口(GPIO)以及复用的其他64个GPIO可用于系统控制。这些复用的GPIO引脚有许多不同的用途,只有当不使用该引脚的主要功能时方可使用GPIO功能。

3 典型应用

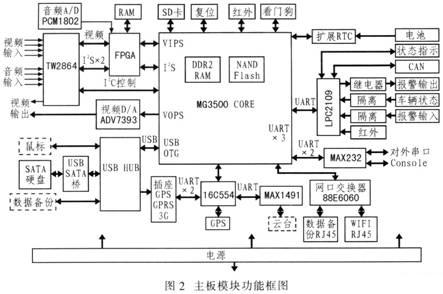

MG3500的典型应用是车载DVR,由于它具有处理多个标准清晰度(SD)数据流的品质的高清(HD)H.264编/解码,同时还提供在IP网络上传输安全视频数据流的广泛网络支持;典型情况下,一个en-ViE编解码器进行108li编码时只要求500mW的功耗,与基于DSP的解决方案相比,这个功耗仅为后者的十分之一。图2为车载DVR的主板模块功能框图,内含线性电源电路、CPU、SDRAM、复位电路、Flash存储模块及FPGA逻辑电路。

变换TW2864非标I2S为标准的I2S,提供1路I2S作为网络对讲,将数据流跟音频输入合并输入到MG3500,音视频输入输出,音视频编码采用TW2864,而音频解码采用TW2864,视频解码采用ADV7393,串口扩展电路,外围RS232,RS422,USB,1路Ethernet,开关量信号检测和输出控制电路,报警量输入输出,工作状态指示。SB通过USB HUB扩展,设备状态指示、报警输入输出、开关量检测、CAN则由ARM7完成。

车载DVR硬件功能方框图由电源板模块、音视频编码模块、音视频解码模块、数据存储模块、对外接口模块、I/O采集模块等组成。

电源板模块是为系统提供可靠的、稳定的电源,提供过压、过流保护;共模、差模干扰滤波等;输出12 V、5 V的电压信号。

音视频编码模块是该系统设计的重点,TW2864实现4路音频和4路视频编码,从TW2864输出的4路27 MHz的BT.656格式的视频流经与FPGA相连的DDRIIRAM缓存后,变为2路54 MHz的视频流输入到MG3500的视频捕获口,由MG3500处理。TW2864将输入的4路模拟音频信号变为数字信号后,经一路I2S口输人到MG3500处理。

音视频解码模块实现图像的实时预览和图像回访功能。视频解码器将CPU输出的数字信号,转换成能够远传的模拟视频信号。

数据存储模块主要包含硬盘和SD卡两部分,实现音视频数据的本地存储,重要的比如报警数据实现硬盘和SD卡的双备份。同时SD卡还可用于程序更新、日志存储、数据读取等功能。

对外接口模块主要包括USB2.0HighSpeed,Ethernet,RS485,RS232等。

应注意的问题:USB的速度是这一部分的瓶颈,Mobilygen公司不支持用户采用扩展器件扩展USB口,因此使用USB HUB。

4 结束语

因为MG3500 SoC具有很多同类产品没有的优点。所以,在应用领域MG3500SoC必将有广泛的应用前景。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。