摘要:时钟数据恢复(CDR)电路是高速数据传输系统的重要组成部分。文章介绍了一种半数字二阶时钟数据恢复电路的基本结构、工作原理和设计方法,并进行了仿真和验证,结果表明,电路能够满足系统设计要求。

1 引言

随着数字系统及网络对计算量和通信速度的要求越来越高,传统的并行数据传输方式在速度上已经不能满足我们的需求,高速串行互连技术得到了越来越多的应用。

高速串行数据收发器的发送器负责将低速的并行数据转换为高速串行数据发到信道上,发送器利用本地锁相环电路(PLL)提供必要的时间参考。信道会对数据进行滤波和叠加噪声。接收器负责接收经信道传输来的高速串行信号,并利用时钟数据恢复(CDR)技术从中提取出相位信息,对时钟数据进行恢复,然后再将恢复出的高速串行数据转换为低速并行数据传送给数字终端。

2 时钟数据恢复系统原理

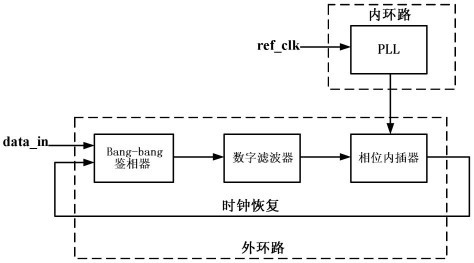

本高速串行收发器采用的是一个半数字的二阶时钟数据恢复系统,如图1 所示。

图1 半数字双环路的时钟数据恢复系统

由图可见,系统由两个环路组成:内环路和外环路。

内环路是一个模拟的PLL,它的参考时钟来自外部输入。内环路的带宽可以设计的很宽,用来有效的抑制内部VCO 噪声,内环路输出一组多相时钟。

外环路是一个数字环路,由Bang- Bang 鉴相器、数字滤波器和相位内插器组成。鉴相器检测输入数据跳变沿和采样时钟之间的相位差。数字滤波器对鉴相器的输出结果进行滤波。内环路输出的多相时钟作为相位内插器的时钟来源,数字滤波器的输出控制相位内插器产生采样钟。外环路的带宽可以设计的很窄,从而有效滤除外部的输入噪声。这就通过双环路解决了单环路的带宽折衷问题。

3 电路设计

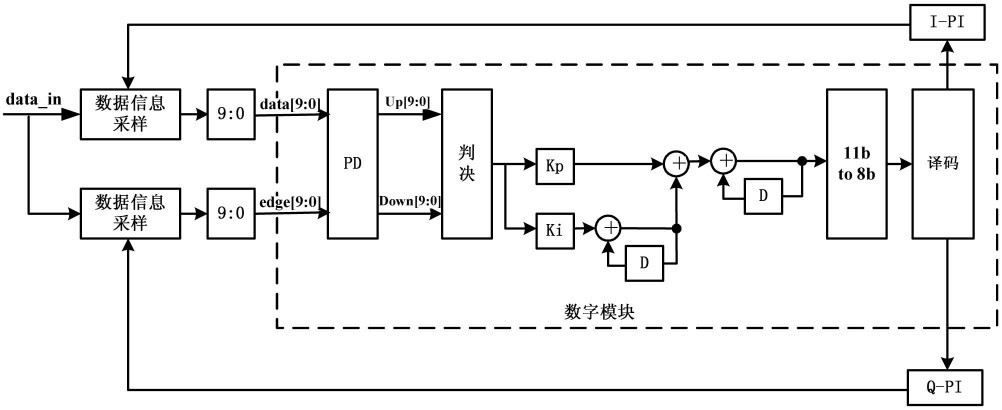

本文主要讨论上述时钟数据恢复系统外环路的设计与实现,具体结构示意图如图2 所示。

图2 时钟数据恢复系统外环路结构图

输入数据经过半速率的时钟采样后转换成两个10 比特的并行数据(data[9:0],edge[9:0]),然后经数字鉴相器比较产生相位判决信息。这个相位判决信息同时送给数字滤波器的比例和积分环节,产生相位控制信息送给相位内插器。

下面将分别介绍数字鉴相器、数字滤波器和相位内插器。

3.1 鉴相器

本设计采用的是数字Bang- Bang 鉴相器,Bang- Bang 鉴相器不同于线性鉴相器,是属于数字电路。它通过检测相位差的极性来判断相位是超前还是滞后。Bang- Bang 鉴相器要使用两个采样时钟:

数据采样时钟和边沿采样时钟。数据采样时钟用于采样数据,它位于数据眼图的中心位置。边沿采样时钟位于数据跳变沿附近。由图2 可以看出,模拟接收端的采样器在采样时钟的控制下完成对高速数据和高速相位信息的采样,并经过串并转换电路输出10位宽数据和10 位宽相位信息,送给本数字鉴相器,比较这两个采样时钟采样到的数据信息,可以判断出相位是超前还是滞后。由于这两个采样电路采用相同的结构,在采样和鉴相之间没有时间偏差,这就克服了传统线性鉴相器存在时间偏差的问题。

鉴相器由五部分组成:寄存器、相位比较器、判决器1、判决器2 和累加器,其中:

寄存器:完成数据和相位信息位的寄存,用于与相应位的比较;相位比较器:对数据和相位相邻两位进行比较(位和位的寄存也要比较),两两比较,总共比较10 次;判决器1:对前5 次比较结果进行判决,判断数据与相位信息是超前、滞后还是同步;判决器2:对后5 次比较结果进行判决,判断数据与相位信息是超前、滞后还是同步;累加器:由于一帧数据分两帧进行判决,将两次判决的结果进行累加得到相位差值,此相位差以数字量的形式输出。

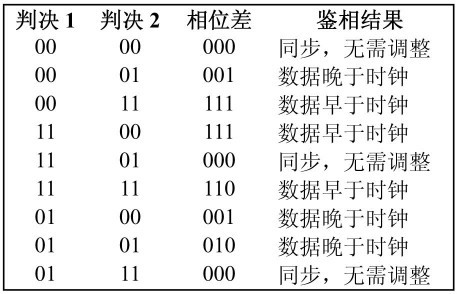

鉴相器的判决真值表如表1 所示。

表1 鉴相器真值表

3.2 数字滤波器

数字滤波器利用累加器来实现模拟滤波器的积分器功能。累加器存储着频率偏差大小的信息,使得环路能够动态地跟踪输入输出之间的频率偏差,从而保证采样点始终处于相位。

数字滤波器可分为一阶,二阶和高阶的数字滤波器。一阶的数字滤波器只包含比例环节。二阶的数字滤波器包含两条支路:比例和积分环节。

本设计采用二阶数字滤波器,其比例系数和积分系数的代码实现如下(其中ph_err 是鉴相器送来的相位差信号):

比例环节由当前的相位判决信息决定,积分环节是以前相位信息的累加,这相当于连续域中的积分,相位的积分对应于频率,从而使积分环节存储着频率偏差大小的信息。环路控制会在每个数字周期都加上这个频率偏差大小的信息,使得采样时钟能跟上频率偏差。

在设计积分环路时,我们的目标是能跟上780ppm 的频率偏差,积分累加器有11 位,只有的6 位直接参与的环路控制。对于积分累加器我们还做了防溢出处理,它的范围在- 1/32UI 和+1/32UI 之间。这样做的好处有两个:一方面是为了防止环路引起振荡,另一方面是防止相位内插器产生毛刺。

3.3 相位内插器

半数字的时钟数据恢复系统利用相位内插器来实现VCO 的功能,相对于VCO 来说,相位内插器的传输函数少了一个积分环节。这一个积分环节被放在前面的数字滤波器中来实现。

相位内插器有多个相同频率的输入时钟,这些输入时钟有着不同的相位。对输入时钟进行相位插值得到输出时钟。相位插值的幅度由数字滤波器送来的控制字决定。它的传输函数是一个比例函数。

在功能实现上,相位内插器相当于一个相位的数字模拟转换器。

4 仿真和测试结果

本高速串行数据收发器芯片采用的工艺是65nm 数字CMOS 工艺。信号传输速率为3.125Gbps。整个芯片的面积大约为400*800μm。

输入数据频率为3.125Gbps,PLL 产生的时钟频率为1.5625GHz,时钟数据恢复系统的数字模块的工作频率为3.125GHz。

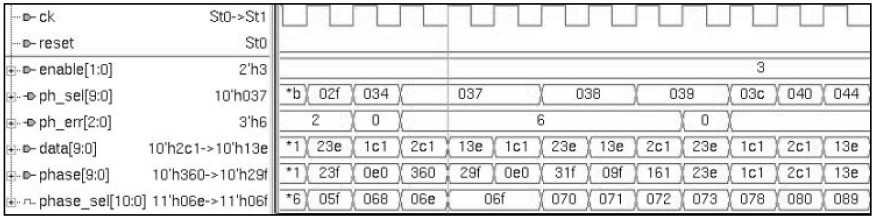

图3 是利用VCS 进行仿真的波形,图中将内部的重要信号显示了出来。

图3 时钟数据恢复电路的VCS 仿真波形

从CDR 仿真验证可以得出,在数字鉴相器、数字滤波器和相位内插器的共同作用下,CDR 能够恢复出数据的相位信息,可以很好的满足系统设计的要求。

5 结论

本文介绍了一种应用于高速串行收发器的时钟数据恢复电路的设计方法,并且在VCS 环境下成功进行了仿真,该时钟数据恢复系统相比较于基于模拟锁相环结构的时钟数据恢复系统,带宽可以做的很窄,特性稳定,对工艺、温度和电压的变化不敏感,且可重用性好。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。