1. 引言

长期演进(LTE)蜂窝标准是3GPP 3G演进的两个组成部分之一,另外一个是HSPA演进。如图1.0所示。LTE无线接入网络(RAN)规范被安排在2008年初完成,随后,一致性测试规范预计在2008年8月准备就绪。

图1.0 3GPP向 UMTS的演化路线

LTE有许多目标,LTE的重点是在整个10年期间内超越UMTS而满足无线用户的各种需要。这包括降低无线用户以及网络运营商的成本;另一方面,以服务差异化的形式提供更佳的各种服务,同时提供更低的延时并提高数据速率。

以服务差异化的形式所提供的各种更佳服务可以通过基于QOS概念的链路自适应来实现。在LTE中,链路自适应超越HSDPA能够提供什么,尽管HSDPA能够在时域上提供链路自适应以响应不断变化的信道条件,但是,LTE也能够提供频率自适应。

在数据速率领域,LTE预期提供100Mbps的峰值下行链路(DL)速率以及50Mbps的峰值上行链路(UL)速率,分别提供5 bit/s/Hz和2.5 bit/s/Hz的频谱效率,这可以利用OFDM与补充的MIMO技术来实现。较低的延时通过扁平的网络架构来实现。所采用的网络架构基于IP (Internet Protocol)以及更短的PHY处理时间,如图2.0所示,另外还具有在LTE的eNodeB (eNB)中实现的各种更高层功能。与UMTS相比,LTE网络架构把沿着数据路径的节点数量从4减少至2。

图2.0 经演化的UTRAN 概观

2. LTE的关键要素

对于上行链路来说,LTE无线接入将基于单载波频分多址(SC-FDMA)[5]。SC-FDMA波形所具有的良好的峰值与平均功率比(PAPR)推动上行链路采用SC-FDMA。利用较低的PAPR,射频

功率放大器(RFPA)的操作可以获得更高的效率,从而使手机的

电池寿命更长。对于下行链路来说,可以采用经典的OFDMA方案。

除了调制之外,另外一个关键要素就是依赖于调度的信道条件的可用性。这容许在共享信道中的时频资源在用户之间动态共享。调度间隔—正如间接提到的—是基于1ms的时分以及180KHz的频分。同样地,在MAC层的调度器的实现是确保下行链路性能的关键要素,因为它决定每一个链路所采用的速率。像存在于MAC层的HSDPA混合ARQ一样,要以多个并行停止和等待ARQ处理的形式采用软组合。混合ARQ方案是基于针对再次发射的增量冗余(IR),除了上述关键要素之外,LTE将把多

天线支持作为该规范不可分割的组成部分。接收和发射分集方案、波束形成以及空间复用都将得到支持。

LTE系统的目标之一就是,它需要允许从2G/3G向LTE的灵活升级。正因为如此,跨越1.25 MHz至20MHz的灵活的频谱分配要可用,且LTE系统应该能够在450 MHz到2.6GHz之间工作。换言之,LTE规范的带宽是不可知的 (Bandwidth agnostic)。

另一点值得一提的是,与UMTS不同,LTE提供FDD/TDD组合和TDD方案、基于单一OFDMA无线接入技术的。TDD方案被称为帧结构2,支持与TD-SCDMA的共存

3. LTE 物理层的关键要素

LTE在利用通用无线接入技术的10ms无线帧的基础上提供两类帧结构。这两类帧结构分别是被称为类型1的FDD/半FDD以及被称为类型2的TDD,它们均基于10ms的无线帧,每一无线帧具有20个时隙,每个时隙占用0.5 ms。类型2帧结构被提供为与TD-SCDMA共存,如图3.0所示。注意,TD-SCDMA帧结构在5ms的子帧内具有10个时隙。这10个时隙当中的3个—DwPTS、GP和UpPTS—是专用时隙,它们在LTE帧结构类型2中被复制。

图3.0 TDD 类型 2 帧结构

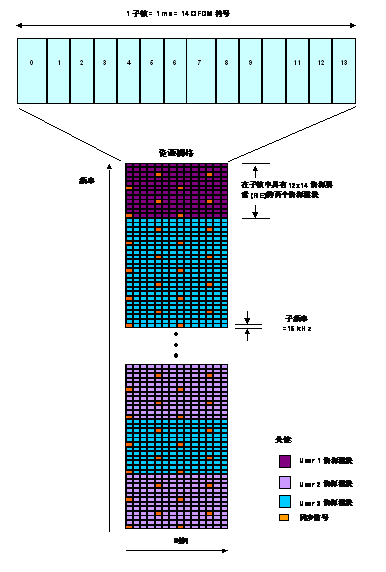

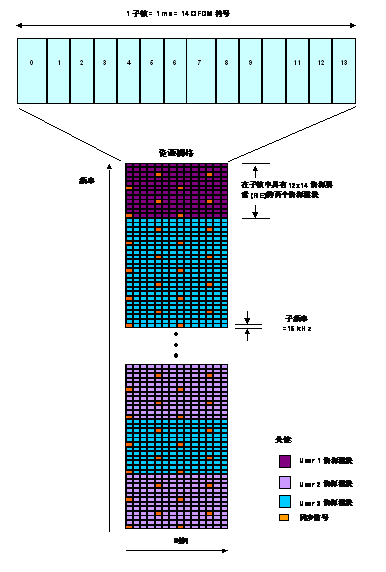

在时域和频域中提供链路自适应的LTE系统的能力就是针对下行链路采用OFDMA方案。这意味着下行链路物理资源是根据一个OFDM子载波以及一个OFDM符号周期来定义的,这就被称为资源要素(RE)。总数84个RE构成一个资源模块(RB),这个资源模块由具有7个OFDM符号的一个时隙(0.5ms)周期上的12个子载波组成。正因为如此,下行链路传输信号根据如图4.0所描绘的资源栅格(RG)被定义为每一个用户拥有对应于两个时隙(1ms)的两个RE。

图4.0用于LTE的下行链路资源栅格

表1.0所描述的关键物理层参数是所分配的频率带宽的函数。

表1.0 DL物理层关键参数

4. LTE基带处理的重要特征

4. LTE基带处理的重要特征

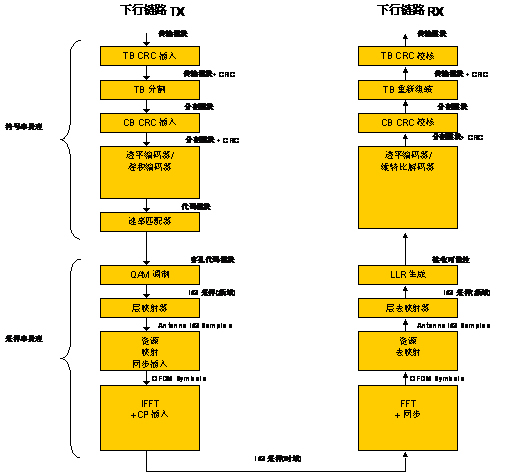

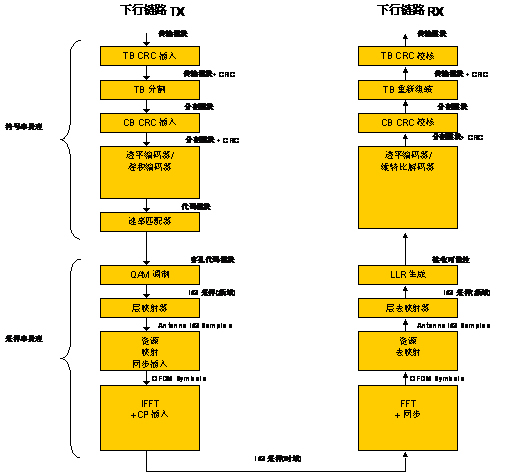

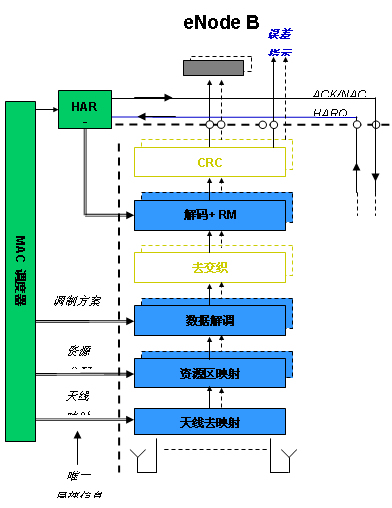

针对Tx和Rx的下行链路物理层如图3.0所示。注意,它可以被分解为两类处理,即符号率处理和采样率处理。从图3.0可见,与基于WCDMA的UMTS标准相比,符号率处理比较简单。

图5.0 3GPP LTE 下行链路处理

正如在UMTS中一样,LTE基站设计所面临的挑战在于上行链路的处理。在LTE的情形下,这进一步结合了短的处理时间要求,以实现较低的延时,与此同时,在Node B具有较之于RNC更高层的功能。

在这一节我们将从微观和宏观两个方面回顾各种挑战以及解决方案。

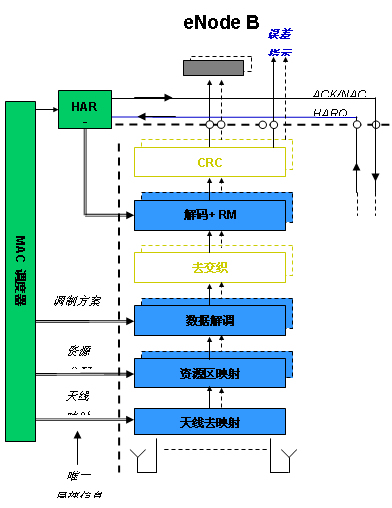

在微观层面,特别是对于如图6.0所示的上行链路信号链来说,LTE延迟预算主要由HARQ往返的8ms延时来定义,也就是说,初传输与再次传输之间的时间。要考虑两倍1ms的传输时间,刚好把6ms留给发送和接收数据。那意味着LTE上行链路处理必须在3 ms以内满足由下列功能提出的延迟预算。它们分别是:

? 信道估计延迟;

? 解调;

? 速率匹配和IR组合;

? 透平(Turbo)解码;

? MAC/RLC处理;

? UL/DL时间偏移量。

图 6.0 LTE 上行链路信号链

假定需要短的处理时间,因此,至关重要的是诸如iDFT这样的、在SC-FDMA解调中所使用的重要模块,以及透平解码必须在尽可能短的时间内完成。赛灵思提供IP核解决方案,使基站设计工程师能够达到iDFT以及透平解码(Turbo Decoding)应用的目标。

以如图7.0所示的iDFT处理为例,经过信道估值,在坏情形下iDFT处理可用的处理时间是40us。赛灵思的iDFT解决方案使所有12的倍数的点长具有由2、3和5构成的素因子,能够满足处理时间的要求。除了FFT/iFFT之外—两个处理用DSP或FPGA均有效,在FPGA中做iDFT有明显的优势,因为DSP的比特反向寻址仅仅适合于基数2。类似地,为了有效地并行实现解码,赛灵思面向具有QPP交织器的LTE的透平解码IP 核,利用400MHz的时钟速度对如图8.0所示的代码模块长度进行8次迭代的情形仅仅花40us的解码时间。

图9.0 FPGA 作为用于LTE的协处理器

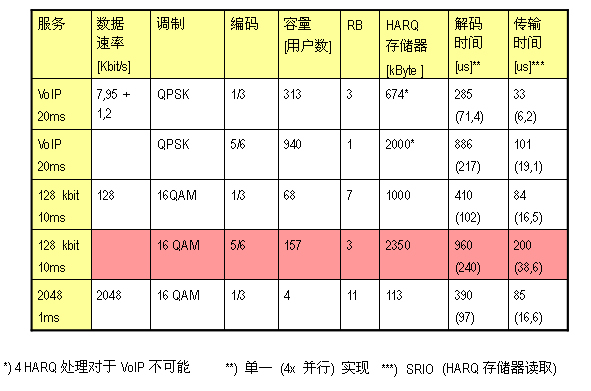

然而,在这里存在的挑战在于因FPGA和DSP之间的互连引起的延迟。我们将采用一个基于常用的SRIO接口的上行链路例子来证明,这个例子具有下列参数:

? 10 MHz带宽、短CP、单一扇;

? 无重发;

? 4 HARQ处理;

? 无空间复用;

? 基于估计的透平解码持续时间;

? SRIO: 3.125 Gb、1x通道、8/10编码、每个拾取器25比特开销;

? 针对DDR2

存储器、200 MHz、32比特只读的传输时间。

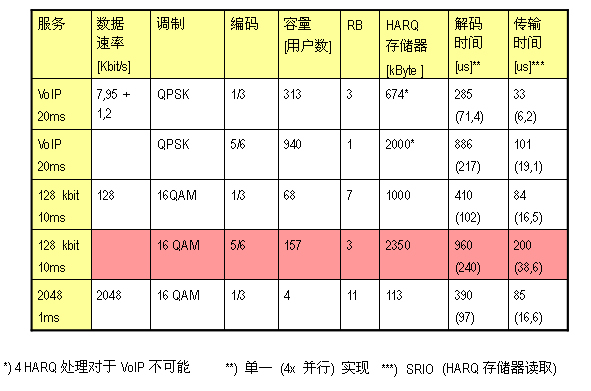

如表2.0中所示为对不同服务—远远好于坏的情形—进行计算的例子,其中,包括必须不超过1000us总时间的编码时间以及sRIO传输的延迟。

表2.0 上行链路处理时间例子

从上表我们可以总结如下:

? 在SRIO传输中发生了重大的延迟;

? 需要并行实现透平编码。

这里的主要问题在于,延时和数据速率要求特别地给利用单一SRIO链路的协处理方法带来了挑战,因为对于20MHz带宽的情形它招致高达400us的延迟,这已经是可用处理时间的40%。

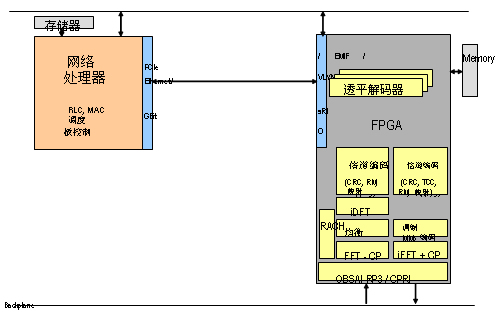

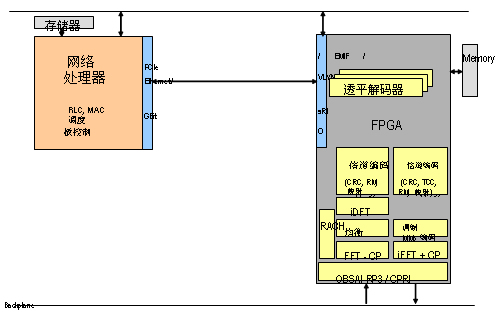

为了解决延迟问题,采用基于FPGA的预处理方法来取代FPGA作为协处理器方法。这意味着需要在FPGA中实现完整的PHY层处理,而DSP处理器担当控制器并完成更高层的各种功能。如图10.0所示。利用对DSP处理器的预处理方法,DSP处理器会取代网络处理器或把网络处理器功能减少至仅仅做集中的PDCP处理以及回程接口。采用这一方法的另一个优势就是FPGA可以被用于MAC加速功能以补偿在DSP上存在的低控制代码性能。另外的方法就是采用FPGA作为对网络处理器的预处理器,如图11.0所示。

图10.0 利用DSP架构实现的FPGA预处理

图11.0 利用网络处理器架构实现的FPGA预处理

总而言之,这两种方法除了克服延迟问题之外,具有若干优势,如为将来规范的各种变化做好准备。

5. Xilinx LTE基带参考解决方案

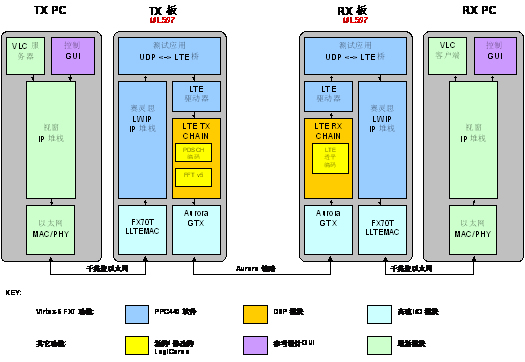

赛灵思近在巴塞罗纳举行的Mobile World Congress 2008上演示了面向PDSCH的、符合3GPP LTE标准的LTE基带下行链路解决方案。

该参考解决方案由各种相关的赛灵思LTE IP核组成,包括透平编码/解码、速率匹配、具有循环前缀插入以及QAM映射器和去映射器的FFT/iFFT。该参考解决方案的下行发送和接收链如图5.0所示。这一参考解决方案也适合对面向LTE的、业已开发完成的各种IP核[3]提供系统级验证。

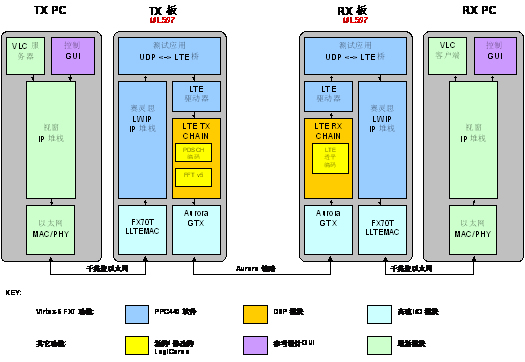

在高于10 MHz的带宽上,赛灵思成功地演示了远远高于100Mbps的视频流。这一成功的演示所采用的面向视频流的参考应用,是基于运行在一台个人电脑主机上的开放源视频局域网服务器(VideoLan Server)。LTE基带参考解决方案位于两个近发布的ML507板上。每一块板通过千兆位以太网链路与主PC通信。由主PC发出的UDP数据包首先由三态以太网MAC模块(TEMAC)处理,随后经过轻量IP堆栈(LWIP),才进入LTE基站参考解决方案的发射(TX)模块。来自TX模块的I/Q 数据通过用于处理的Aurora链路,被输出至具有LTE接收(RX)功能链的另一块ML507板上。

图12.0显示了在MWC 2008上的设置,而图13.0描绘了赛灵思LTE基带参考设计演示平台的各个模块。

图12.0 赛灵思LTE基带参考设计演示

随着LTE基带参考设计的发布,赛灵思再次证明了在无线解决方案领域的领导地位,并进一步致力于支持基站供应商开发满足更高比特率、更低延迟以及更高灵活性(由于目前LTE标准的不断演进,这一点特别重要)的LTE解决方案。

图13.0 赛灵思LTE基带参考设计系统结构图