半导体技术是以半导体为材料,制作成组件及集成电路的技术。随着半导体技术的不断进步和集成技术的发展,微处理器的集成度越来越高。为了获得高效率,微处理器的驱动电压呈低压化走势。从原来的33V降到l.8~l.lV左右,终将降到0.6V.另一方面,微处理器的功能越来越强大,其内部功能电路也越来越多,其要求驱动电流也越来越大,从以前的13A到目前的30~50A,以后将达到100A.面对这种趋势,48V电压总线的分布电源系统相对于12V电压总线的分布电源系统将更适合。

对于48V输入电压和lV左右的输出电压,变压器的应用就变得十分必要。对于几十A甚至上百A的变压器副边电路的输出电流,倍流是一个非常有效的方法,因为,它一方面可以减小变压器副边和电感器上电流的有效值,另一方面还可以减小电流纹波,从而减小输出电压的纹波值。

然而,变压器加上两个倍流输出电感,若采用单独的磁性元件将会占用相当大的体积,则与提高功率密度这个目标相背离。

若采用磁集成技术,将变压器和电感集成在同一磁芯上,将会大大减小体积从而提高了功率密度。

在集成输入滤波电感与倍流输出电感的推挽正激变换器中,将输入电感、变压器、倍流电感集成到同一个磁芯上,则可在获得良好的输入、输出效果的同时,还拥有很高的功率密度。

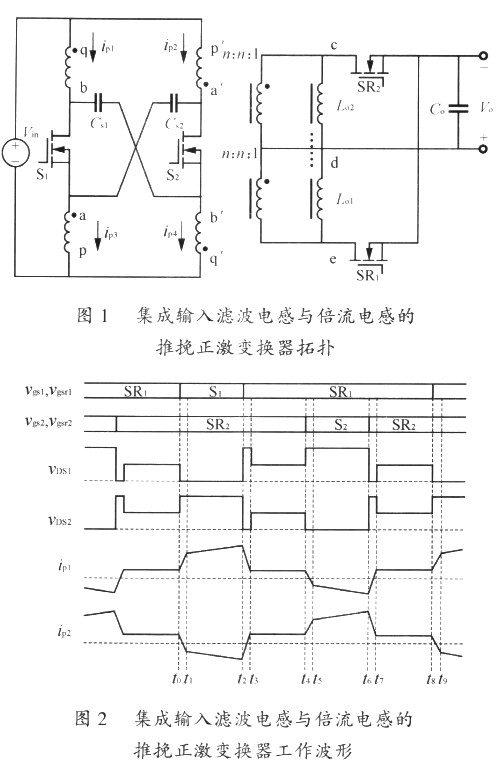

1 集成输入滤波电感与倍流电感的推挽正激变换器

集成输入滤波电感与倍流输出电感的推挽正激变换器拓扑如图l所示。它的工作波形如图2所示。在原边电路中Cs1和Cs2与变压器原边绕组的漏感构成输入滤波器。ip1与ip2相互叠加构成平缓的输入电流。在副边,变压器的副边绕组作为倍流电感。本电路的具体工作过程分析如下。

1)[t0-t1]t0之前S1、S2关断,t0时刻S1开通,绕组qb和ap一起承受正电压Vin绕组p'a'、b'q'承受反电压大小为2Vcs-Vin=Vin,Vds2大小为2倍Vin.Cs1及Cs2通过S1放电。ip1及ip3增大,ip2及ip4减小;设I0为负载电流,Ia为漏磁平均电流,Imag为磁化电流,n为变压器变比。当ip1及ip3由Ia增大到![]() 时此过程结束.

时此过程结束.

2)[t1-t2]S1开通S2关断,

绕组qb和ap一起随正电压Vin,而绕组p'a'、b'q'承受反电压大小为Vin.

绕组qb和ap一起随正电压Vin,而绕组p'a'、b'q'承受反电压大小为Vin.

3)[t2-t3]t2时刻S1关断。此时漏感要释放能量,S2体二级管导通,提供ip1及ip2续流回路,此时线圈qb和a'p'一起承受Cs1上的电压,ip1减小,ip2增大。ip3、ip4与ip1、ip2变化情况一样。当ip1=ip2;ip3=ip4时这个阶段结束。

4)[t3-t4]在这整个时间段内,ip1=ip2=ip3=ip4=Ia,其中ip1、ip4共同沿着qb-Cs1-b′q′支路;ip2、ip3共同沿着p′a′-Cs2-ap支路。绕组qb,b′q′,ap,p′a′承受零电压。

5)[t4-t8]此时间段电路工作过程分析与[t0-t4]时间段相同。输入电流iin=ip1+ip2可以知道,通过ip1和ip2纹波的相互抵消可以得到平缓的iin.而不需要加入输入滤波电感,即在输入端集成了输入滤波电路。

2 磁集成部分的分析与PSPICE仿真

2.l 磁导一电容类比建模法

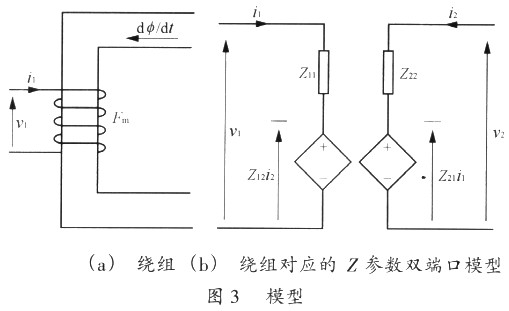

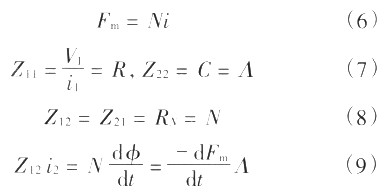

在分析磁性元件时,人们一般是通过磁路一电路对偶变换法来进行的[2].但是它不能够直接反映出磁件的电路参数与磁路参数的特性[2].为此人们提出了另一种分析方法,即磁导一电容类比建模法[2].对于二端口绕组磁导电容类比建模法用一个Z参数双端口模型来表示。如图3所示,图3(a)表示二端口绕组,图3(b)表示Z参数双端口模型.

图3(a)中各参数说明如下:V1是绕组两端的的电压;i1是绕组上的电流;绕组匝数是N;R是绕线电阻;磁动势为Fm.下面来确定图3(h)中的参数。

首先确定Zt2.

假设 ,那么我们可以令

,那么我们可以令

Z12=N (1)

式中:N为绕组的匝数。

则

式(2)正好反映了线圈内磁通变化产生的感应电动势。那么参数Z11的确定就可通过设 来确定。

来确定。

Z11的大小就是绕组的电阻R.

现在假设Z21=Z12

那么Z21i1=Ni1 (4)

式(4)正好表示了绕组通过电流时产生的磁动势。

来确定Z22.

我们将V2端口短路。

则Z21i1=-Z22i2(5)

因为

所以Z22=A(A是磁芯的磁导)。

由此我们可以通过以下变化得到与图3对应的图4.

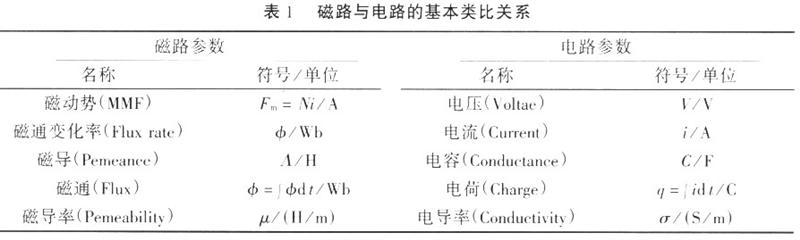

磁路与电路的基本类比关系如表1所示采用磁导一电容类比建模法能够直接建立起磁性绕组的电路模型,有利于简便地分析复杂的磁件,而且使磁件的仿真通过电路的仿真来实现。

2.2 推挽正激变换器磁集成部分Z参数模型的建立

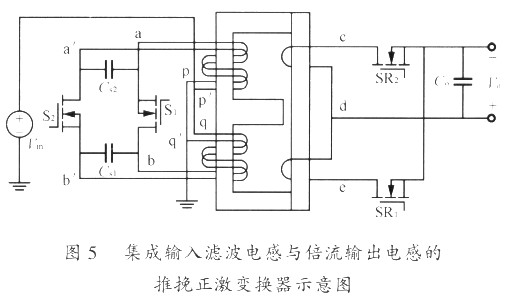

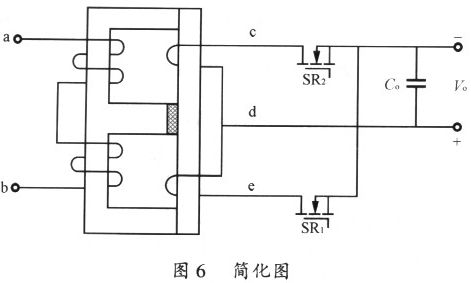

图5是集成输入滤波电感与倍流输出电感的推挽正激变换器示意图。通过图5,我们知道集成输入滤波电感与倍流输出电感的推挽正激变换器磁件的磁芯为EI型,原边有两组中心抽头绕线,副边为一组中心抽头绕线。原边既作为变压器的原边,它们之间的捅感又作为输入滤波电感,副边既作为变压器的副边,又作为倍流输出电感。为了简化分析,取原边的一组绕组和副边绕组束作分析。如图6所示。

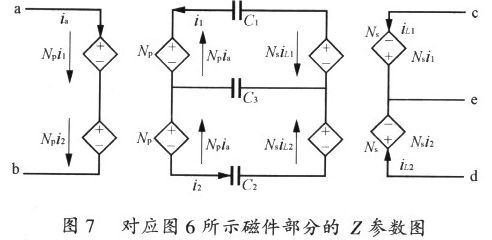

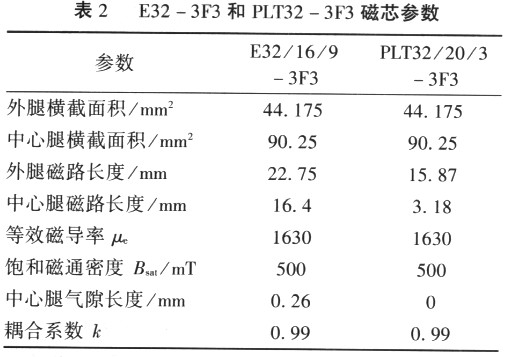

根据前面分析可作出图6的等效Z参数图。如图7所示。

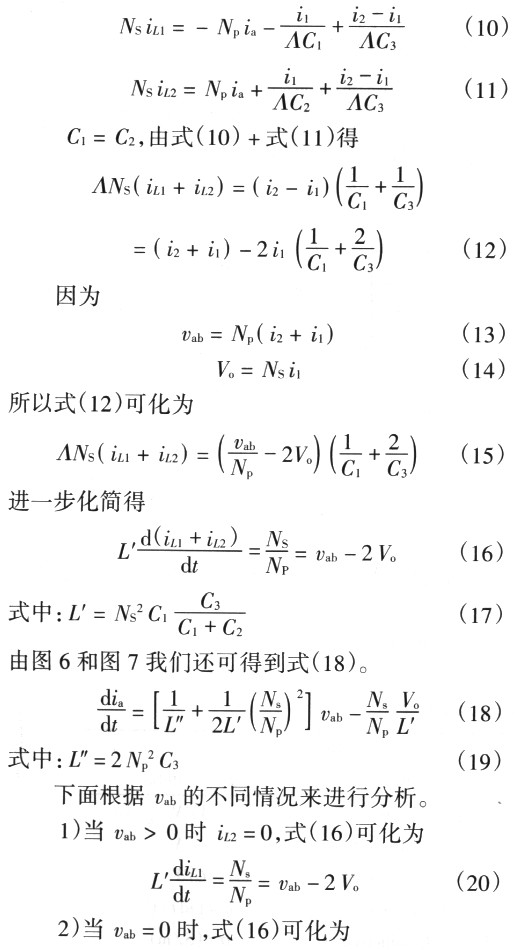

根据上述3种情况的分析和满足伏秒平衡,对于图5所示的变换器稳态时满足:

式中:D为开关管的导通时间除以1/2丌关周期。

2.3 推挽正激变换器磁集成部分的PSPICE仿真

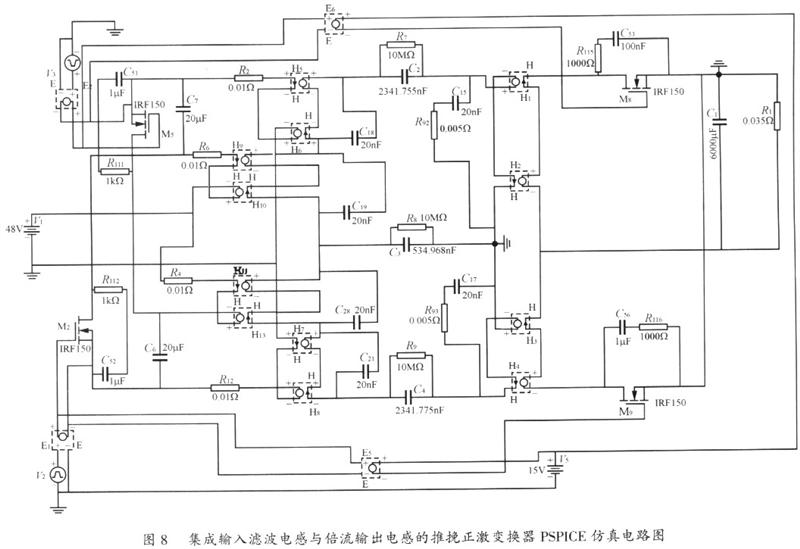

假设集成输入滤波电感与倍流输出电感的推挽止激变换器的输入电压为48V,输出电压为1.2V,输出电流为40A.我们采用Z参数等效模型来进行它的PSPICE仿真。

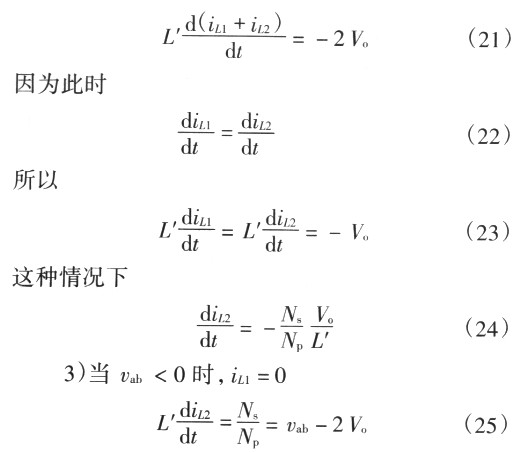

我们选取一对E32-3F3和PLT323F3磁芯。它们的各个参数如表2所列。

根据表2可求得C1=C2=2341.755nF

C3=534.968nF

取Np=4,N8=1

结合式(17)和式(19)

求得L′=0.367μH

L″=17.118μH

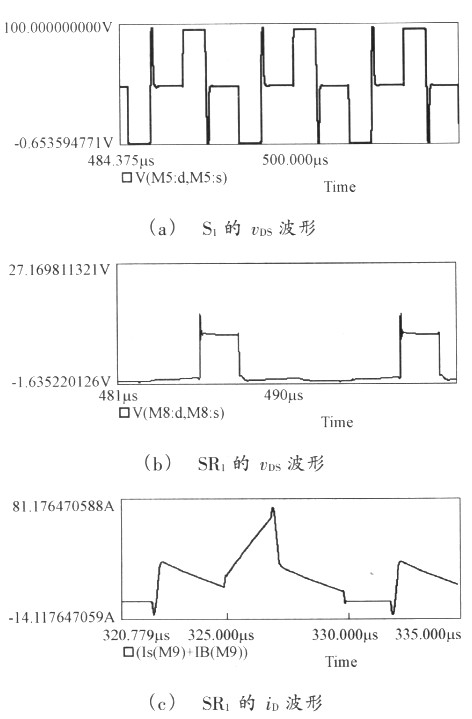

集成输入滤波电感与倍流输出电感的推挽正激变换器PSPICE仿真电路图和仿真波形如图8及图9所示。

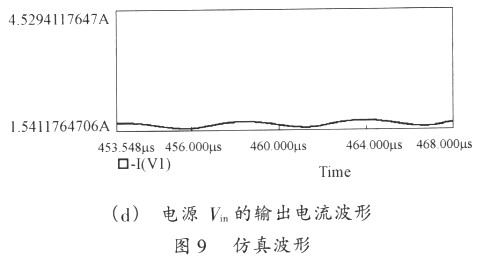

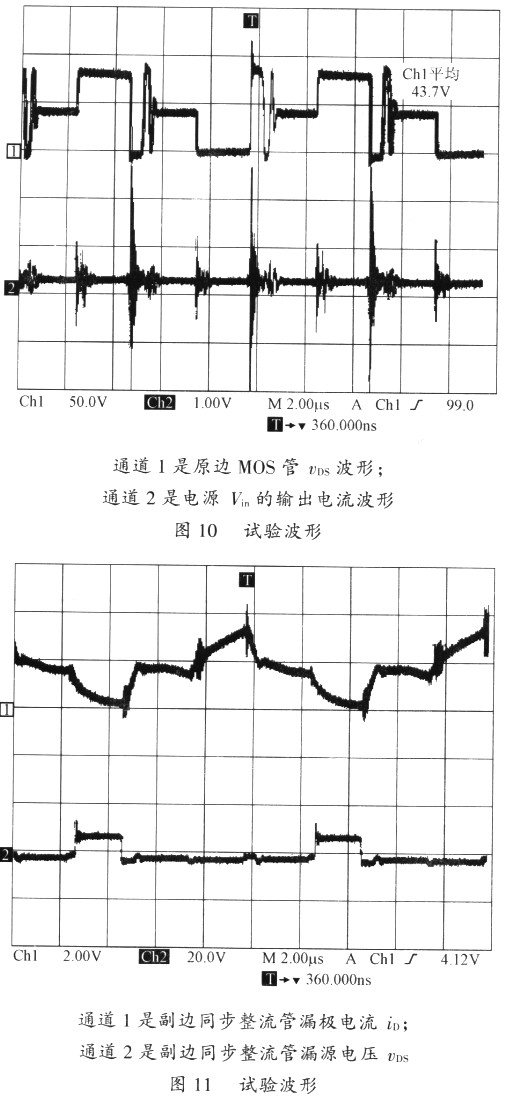

3 实验结果

根据上面的分析和方针,设计输入48V,输出1.2V、40A的正激变换器。实验结果中电流波形通过霍尔元件测得。图10通道2是电源Vin的输出电流波形,测量电阻120Ω,电流转换比是1:1000,图11中通道l是副边同步整流管漏极电流的波形,测量电阻82il,电流转换比是l:1000.

从实验波形中可以看出,试验结果与仿真分析相吻合。

4 结语

通过仿真和实验证明集成输入滤波电感与倍流输出电感的推挽正激变换器,利用变压器的漏感而不需单独的电感作为输入滤波电感,而倍流输出电感也通过变压器的副边绕组来实现。这样,整个电路体积大大减小,而且相对于分立电感的结构来说,损耗也小,噪声源也少。由于本拓扑的磁什结构比较复杂。为此,我们采用磁导一电容类比建模法来进行分析。这种方法能够直接用电路参数来描述磁件,包含磁件的电路可以全部用电路参数来描述。这样整个电路分析容易,且便于PSPICE仿真。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。