1 引言

由于是对射频信号直接进行采样,结构简洁,并把模拟电路部分减小到限度,无疑是理想的方式,但这种结构不仅对A/D转换器的性能如转换速率、工作带宽、动态范围提出了非常高的要求,同时对后续DSP或ASIC的处理速度要求过高,以至于无法实现;宽带中频采样的软件无线电结构与目前的中频数字化接收机(发射机)的结构是类似的,都采用了多次混频体制,在适当的中频位置进行数字化。

软件无线电的基本思想是以一个通用、标准、模块化的硬件平台为依托,通过软件编程来实现无线电台的各种功能,从基于硬件、面向用途的电台设计方法中解放出来。功能的软件化实现势力要求减少功能单一、灵活性差的硬件电路,尤其是减少模拟环节,把数字化处理(A/D和D/A变换)尽量靠近天线。软件无线电强调体系结构的开放性和全面可编程性,通过软件更新改变硬件配置结构,实现新的功能。软件无线电采用标准的、高性能的开放式总线结构,以利于硬件模块的不断升级和扩展。

2 单信道软件无线电数学模型

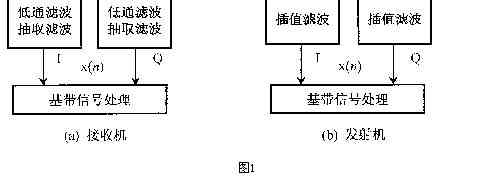

单信道软件无线电接收机和发射机的数学模型如图1所示。以接收机为例,将数字处理流程分为两部分:一是数字下变频部分,包含NCO、混频器、低通滤波以及抽取滤波器;二是基带信号处理部分,包含解调、译码、自适应均衡、帧调整、比特调整和链路去加密等算法。数字下变频单元的功能一是进行频谱搬移,将射频信号或中频信号转换为零中频信号;二是降低采样速率,将满足射频或中频采样定理的高速采样信号降低为低速基带采样信号。

就目前器件的发展水平,要想实现完全的射频数字化,几乎还不太可能,所以研究的重点往往放在中频数字化上。根据上面的分析,中频数字化中基带信号处理部分由于处在较低速率上,一般采用通用DSP方案实现,通过软件来实现各种功能;而对于数字变频部分,它们过高的速率使得通用DSP无能为力,即使像运算速度已高达600 MHz的TMS320C64X也不能解决数字中频的处理。目前,人们已经提出了一些解决关键元器件的方法,并已出现了大量的数字中频产品,像Harris公司的可编程数字上/下变频器HSP50415、HSP50216等都为软件无线电的实现奠定了良好的基础。同时,在另一方面,由于FPGA技术的迅速发展,超大规模、高速度的FPGA芯片不断出现,为实现高速数字信号处理提供了可能,这种FPGA加DSP的设计方法为实现软件无线电提供了一种更加灵活的方案。

3 几种技术方案的比较

3.1 FPGA的发展现状

FPGA(Field Programmable Gate Array)现场可编程门阵列是近10年发展起来的新型可编程逻辑器件。由于FPGA器件的功能由逻辑结构的配置数据决定,工作前需要从芯片外部加载配置数据。配置数据存储在片外的EPROM或其它存储体上,人们可以控制加载过程,在现场修改器件的逻辑功能,即所谓现场编程。FPGA与CPLD一起在数字电路中发挥着巨大的作用。 FPGA技术的发展可以从的FPGA生产厂商Xillinx公司推出的产品看出,无论是在规模、处理速度还是功耗上,都得到了长足的进步

3.2 FPGA与ASIC的比较

下面我们从功耗、体积、成本、现场可编程性以及硅芯片的解决方案等角度分别对高速DSP、ASIC以及FPGA设计方案进行比较,如表1所示。

从表1中可以看出,与ASIC设计方案比较,FPGA具有更大的灵活性。ASIC设计是在集成电路界被认为是一种为专门目的而设计的集成电路。设计系统直接使用可重构的FPGA,不但增加了设计的灵活性。

3.3 FPGA与DSP的比较

DSP芯片,也称数字信号处理器, 是一种具有特殊结构的微处理器。DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP指令,可以用来快速的实现各种数字信号处理算法。但要达到千兆赫量级的时钟速度所要求的功耗仍然较高,并且其串行处理的结构不可能实现高阶的数字滤波器功能(如表2所示)。

4 FPGA在数字中频处理中的应用

根据图1所示数学模型,FPGA在软件无线电中的应用主要体现在数字上变频DUC和数字下变频DDC中。经过A/D采样后的信息直接送给FPGA,在FPGA中完成本地混频,把中频信号搬移到基带信号,然后经过低通滤波和多级抽取滤波,降低信息的采样速率,由FPGA送至通用DSP,实现基带信号的调制解调;对于数字上变频结构,和下变频有完全对称的结构。

4.1 本地频率产生器和混频器

DDC结构中个环节就是要实现本地数字混频,主要由两个部件完成,一是乘法器,二是数控振荡器(NCO)。乘法器是数字信号处理中的基本运算单元,在FPGA中设计较为复杂,而且占用资源也比较多,但在具体实现FIR滤波时,往往不采用这种直接的乘累加的形式,以免占用大量的资源;在实现混频时,由于只需两个乘法器,而且是在很高的速率下进行,所以不考虑资源的限制。

NCO的硬件结构如图2所示,主要由相位累加器和SIN/COS表构成。相位累加器产生的相位作为地址去查找ROM表,查到的SIN/COS值即本地载波的数字频率送至乘法器,完成混频。在实现NCO时有以下参数值得注意:

· NCO产生数字频率的。此参数与SIN/COS 值的位数有关,位数越宽,则也就越高,但占用FPGA的资源也就越多。

· 载波的同步。如果需要本地载波做到严格的同步,则需要额外的锁相环结构获取偏移相位,进行调整。

· NCO输出频率的噪声。噪声的产生与频率在时间上量化有关,由于采样时刻不一定严格对齐载波的相位,所以会产生噪声,但构造更大的正弦或余弦表会减少噪声分量,这同样会增加FPGA的资源占用。

4.2 抽样率变换滤波器组

下变频过程中经过混频后的信号必须进行抽取滤波,以便降低抽样速率,使得通用的DSP对基带信号处理时有充足的时间完成运算;同样,在上变频过程中,首先要进行插值滤波,提高抽样速率,从而实现在IF范围内频谱的搬移。 根据DDC总抽取因子的大小,我们把数字下变频分为两类:即当抽取率大于32时,认为是窄带下变频,反之则认为是宽带下变频。无论是宽带还是窄带,一般都采用FIR结构实现抽取滤波器,但对于窄带下变频,由于抽取因子较大,所以其抽取滤波器组也更为复杂一些,对窄带下变频作如图3设计,其中CIC滤波器为整系数滤波器,滤波时无需乘法运算,而半带滤波器有一半系数为零。

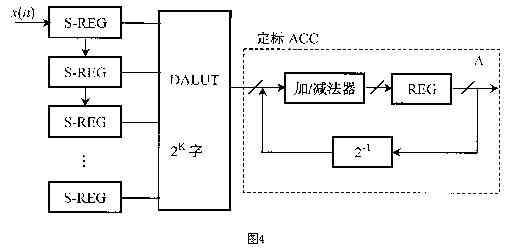

实现FIR滤波功能的基本元素包括乘法器、加法器、延迟单元以及存储单元等,其中乘法器的设计为复杂。用FPGA技术作乘累加运算通常有移位相加、加法器树、查询表和逻辑树等设计方法,不管采取哪种方法,要实现一个高阶的数字滤波器都将占用相当大的资源。相比较来说,采用分布式运算DA算法(Distributed Arithmetic)的FPGA设计无论是在逻辑资源占用上,还是处理速度上都具有很大的优势,特别是对于基于SRAM结构的FPGA更加适合于DSP功能的设计。随着大规模集成电路技术的发展,特别是可编程逻辑器件的发展,DA算法在数字滤波器硬件设计中的研究进一步加强,SDA(串行DA)算法和PDA(并行DA)算法已成为FPGA实现DSP功能为有效的方法。根据DA算法设计的思想,我们进行FIR滤波器设计如图4所示。

图4为FIR滤波器实现的串行DA形式,其中S-REG为串行移位寄存器,实现输入数据的并/串转换,并由TSB(Time-Skew Buffer)完成数据的移位缓存,产生访问DALUT的地址;查表后得到的输 出数据由定标ACC单元完成累加,累加的结果即为滤波后的值。 SDA算法处理的速度与抽头系数的大小无关,只与输入信号的数据位数有关,PDA(并行DA)算法可相应提高信号处理的速度,但它是以牺牲更大的逻辑单元为代价的。为了实现较高性能的滤波器指标,往往需要很多个抽头,这时DALUT必然会占用很大的空间。

4.3 FPGA实现和实验结果

如图5所示,中频A/D、D/A分别采用AD公司的AD9224和AD9764,其中AD9224分辨率为12bit,AD9764为14 bit,采样速率为30.720MHz;DSP选用TI公司的TMS320C5410芯片,处理速度为100MIPS;音频A/D、D/A由TLV320AIC10实现。该芯片主要完成抽取率为512的DDC功能和插值率同样为512的DUC功能,而且是在同一片FPGA中实现。FPGA单元与DSP接口的数据速率为60kHz.FPGA开发工具为Xilinx Foundation3.1,编程语言采用VHDL和Schematic混合设计方法,并利用CORE Generator提供的DA FIR滤波器方便地实现半带滤波器和整形高阶FIR滤波器功能。

5 结束语

研究表明,这种基于FPGA/通用DSP的协同设计方法,无论是在性能价格上,还是在设计的灵活性上,都有很大的优势,非常适合目前软件无线电硬件平台设计。廉价和方便的优点可以在市场上占据很大的竞争力。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。