摘要:为了减小射频LDMOS器件中场极板寄生电容,提出一种具有分布式源场极板结构的射频LDMOS器件,给出了器件结构及工艺流程。借助微波EDA软件AWR对场极板进行了三维电磁仿真优化设计。仿真及测试结果表明!所设计的分布式源场极板结构在不影响器件击穿电压的条件下,能有效减小LDMOS器件寄生电容!提升器件增益#效率及线性度等射频性能。

0.引言

由于具有高功率增益#高效率及低成本等优点,射频LDMOS(lateral diffused metal oxide semicONductor transistor)器件被广泛应用于移动通信基站、雷达、导航等领域。为了提高LDMOS击穿电压!增大输出功率,采用了各种各样的改进结构,如SUPER-JUNCTION、漂移区变掺杂、RESURF和表面形成G降场层技术等,其中为常用且简单有效的工艺方法就是在漂移区上部使用金属场极板。场极板电容作为LDMOS器件寄生电容的主要组成部分,是决定器件功率增益及截止频率的一个重要因素。

为了解决常规金属场极板结构LDMOS(CFP-LDMOS)器件寄生电容大的缺点!本文提出分布式金属源场极板结构LDMOS器件(DFP-LDMOS)分布式源场极板结构在工艺上易于实现,并在不影响器件击穿电压的前提下,能有效减小器件寄生电容,提升器件射频性能。

1.器件结构及工艺流程

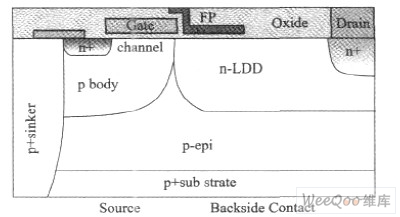

图1所示为射频LDMOS器件剖面图,本文所设计的DFP-LLDMOS器件以传统LDMOS器件结构为基本框架,并应用了分布式金属源场极板技术。

图1 射频LDMOS器件剖面图

全文PDF:

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。