开关电流技术是近年来提出的一种新的模拟信号采样、保持、处理技术。与已成熟的开关电容技术相比, 开关电流技术不需要线性电容和高性能运算放大器, 整个电路均由MOS 管构成, 因此可与标准数字CMOS 工艺兼容, 可与数字电路使用相同工艺并集成在同一块芯片上, 这预示着它将在数模混合集成电路的发展中扮演重要角色. 但是开关电流电路中存在一些非理想因素, 其中时钟馈通误差尤为突出, 它直接影响到电路的性能。近年来, 国际上已提出了一些减少时钟馈通误差的技术方案, 例如虚假补偿技术、全差分结构、多相复杂时钟算法存储单元, 大部分都是在输出端产生额外的误差电流来抵消前面产生的误差, 由于独立信号和补偿部分的存在, 复杂的电路和时钟相位技术将不可避免。文中通过分析代SI 存储单元时钟馈通误差产生的主要因素, 提出了一种消除钟馈误差的新方案, 在此基础上完成了电路设计, 给出了仿真性能和对比结果。该存储单元可用于构造性能良好的双线性积分器, 作为滤波器、∑-△ 调制器等系统的基本模块。

1 时钟馈通误差分析

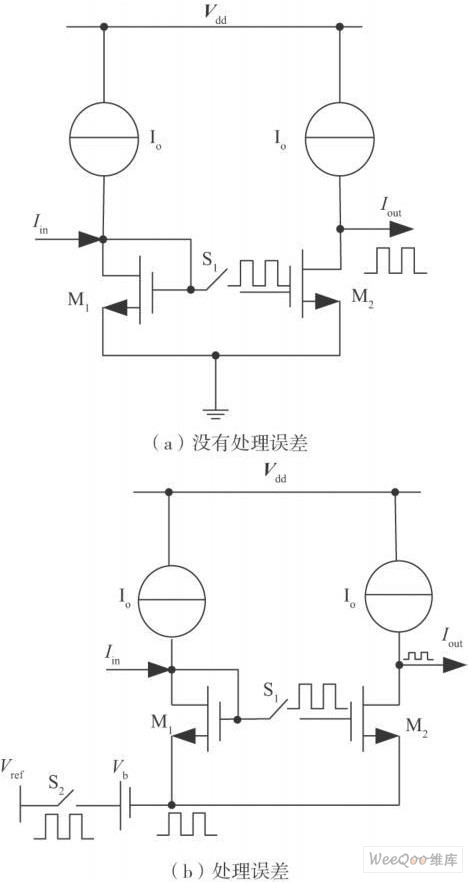

图1( a) 是一个基本的代SI 存储单元, 开关S1 受时钟脉冲信号控制。当S1 断开时, 产生的注入电荷将注入到存储管M2 的栅极, 导致M2 的栅极产生一个时钟馈通误差信号, 终在输出端产生误差电流。图1( b) 是一个含有处理误差信号的存储单元, 它比图1( a) 多了一个电压跟随器Vb 和一个与开关S1 受相同时钟脉冲信号控制的开关S2 。

图1 代开关电流存储单元

图1( b) 工作原理如下:

在采样相位期间, S1 和S2 同时导通, M1 和M2的源极电压相等, 即:

同时它们的栅压也是相等的。因此, 假定M1和M2 的漏极电压相等, 忽略沟道调制效应, M1 的漏极电流I D1 = I in + I O , M2 的漏极电流I D2 =[K 2 / K 1] ID1 , 其中K i 表示两个晶体管的跨导参数;I in和I out 分别表示输入和输出信号。

在保持相位期间, 开关S1 和S2 同时断开, 由S1产生的误差电荷将注入到M2 的栅极, 使得M2 的栅压变为:

同时由S2 产生的误差电荷将在电压跟随器Vb的输入端转化成误差电压, 通过电压跟随器在M2的源极产生误差电压V SCFT2 , 使得M2 的源极电压变为:

其中VGs amp2 和VS samp2分别表示开关同时导通时M2的栅极电压和源极电压; V GCFT2 和VSCFT 2分别表示开关同时断开后在M2 的栅极和源极产生的钟馈误差电压。

结果在保持相位期间M2 的栅源电压保持为:

其中VGSs amp2 表示采样期间M2 的栅源电压; VGSCFT2表示保持期间M2 的栅源钟馈误差电压。

如果选用相同的开关和时钟脉冲控制信号, 并使电压跟随器中使用的MOS 管与M2 的宽长比相同, 那么V GSCFT2 就可能降为零, 从而消除了时钟馈通电压误差, 在输出端阻止了误差电流的产生。

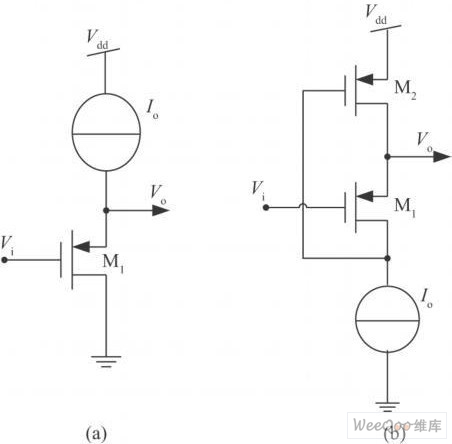

2 电压反转跟随器( FVF)

图2( a) 是一个共漏放大器, 通常被用来作为电压缓冲器。忽略体效应, 输出电压V o= Vi+ V SGM1 ,该电路可以从负载中吸取大电流, 但它的吸取能力受偏置电流源I O 的限制, 流过晶体管M1 的电流受输出电流的影响, 因此V SGM1 是动态变化的, 对阻抗负载来说, 小信号和大信号电压增益都小于1。

图2 电压反转跟随器电路

图2( b) 即为电压反转跟随器( FVF) 电路。

其优点是: 通过M1 的电流保持不变, 不依赖于输出电流。忽略短沟道效应, VSGM1 保持不变, 电压增益为1。该电路可以吸取大电流, 大的吸取能力是因为输出节点的阻抗非常低, 输出阻抗为: r o =1/ ( gm1 gm2 ro1 ) , 其中gmi和roi 分别是晶体管Mi 的跨导和输出阻抗。

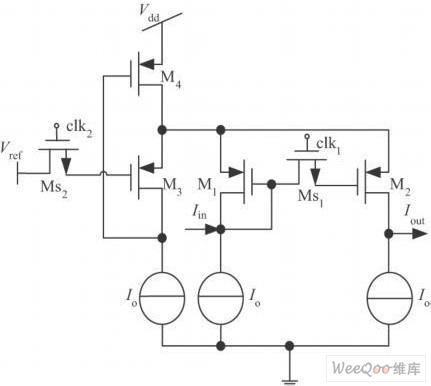

3 高性能开关电流存储单元

图( 3) 即为含有电压反转跟随器( FVF) 的开关电流存储单元。其中M1 、M2、I O、MS1组成基本的存储单元, M3、M4、I O、V ref 组成电压反转跟随器。为了消除电荷注入误差, 设置NMOS 开关MS1和MS2 的宽长比相等, M1、M2、M3 的宽长比相等, 时钟脉冲信号clk1 和clk2 相同, 从而保证了M3源极产生的误差电压VSCFT3 等于M2 栅极产生的误差电压VGCFT2 , 使得M2 的栅源时钟馈通误差电压VGSCFT2 近似为零, 避免了输出端误差电流的产生。

图3 高性能开关电流存储单元原理图

图( 4) 给出了高性能开关电流存储单元的具体实现电路。其中电源电压Vdd为1.8 V, 参考电压Vref 为0.8 V, 偏置电压VP 为0. 4 V, Vn 为1.2V. 晶体管M5~ M10组成两级级联的共源共栅电流镜, 其目的是增大该电路的输出阻抗, 从而有效降低开关电流存储单元的传输误差。clk1 和clk2 采用相同的时钟控制信号, I in和Iout 分别表示输入和输出信号。

图4 高性能SI 存储单元电路图

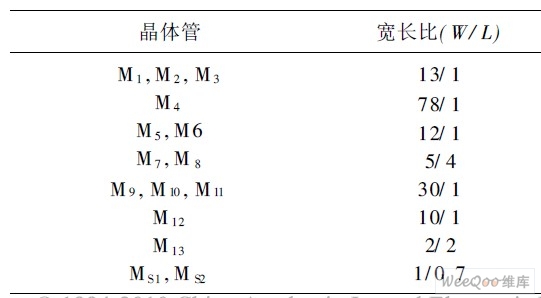

表1 各晶体管的宽长比

4 性能对比

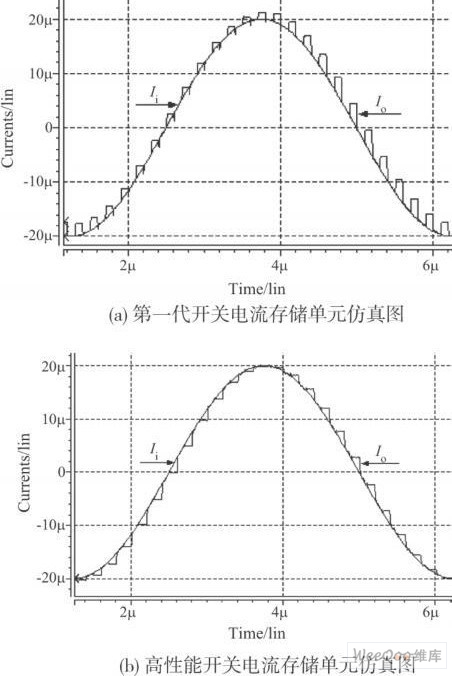

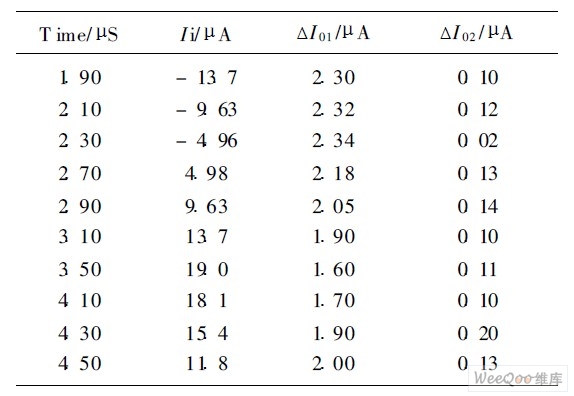

基于0.18 mCMOS 工艺, 分别对代开关电流存储单元和高性能开关电流存储单元仿真, 输入电流为20 A, 200kHz 的正弦信号, 采样频率5 MHz, 仿真结果见图5。表2 中给出了二者的误差对比, 其中I i 表示t 时刻的输入电流, △I O1为代开关电流存储单元产生的误差电流, △I O2 为高性能开关电流存储单元产生的误差电流。由表中数据可以看出, 高性能开关电流存储单元产生的平均误差仅为代开关电流存储单元产生的平均误差的6% 。

图5 代开关电流存储单元仿真图

表2 误差对比

5 总结

本文采用一种新方法, 避免了传统的补偿存储晶体管的漏极电流误差, 转而直接消除存储管栅源的电压误差, 从而保证输出端不会出现误差电流。在AMPI0 18 mCMOS 工艺下, 设计了一种低压、低功耗、低误差的新型高性能开关电流存储单元 。仿真结果表明, 该电路功耗低, 高, 误差仅为代存储单元的6%。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。