嵌入式系统可以用各种微处理器代替通用计算机的CPU,实现既定功能并驱动显示系统以方便人机交流。早期的单片机由于低时钟频率(小于5 MHz)和低I/O口数量的限制,一般只驱动像素比较少(5 000像素以内)的液晶显示器[1-2]。近年来随着制作工艺的发展和设计结构的优化[3],单片机的时钟频率和I/O口的数量都得到了很大提高,低耗能低电压单片机不断出现[4],新调试技术使开发过程效率更高[5],驱动几千像素的液晶显示器早已出现。然而,更友好的人机界面需要更高分辨率的液晶显示器。考察目前流行的液晶显示器驱动方式可以看到,无论使用何种单片机或作为嵌入式系统的微处理器,都会被液晶显示器的驱动控制部分占据大量资源,这就给单片机的性能带来了巨大的挑战。例如三星某显示器模组,分辨率为800×480,输入时钟要求为32.24 MHz~48 MHz,这样的要求使得单片机力不从心。本文研究并开发一种面向嵌入式系统的通用显示器。它以类似于通用计算机的显存存储图像数据,以FPGA控制并读/写显存中的数据,控制液晶屏的驱动。嵌入式微处理器仅需要在改变图像时输出数据,这样,其他时间便可全部空出,用于控制其所在的自动化系统。

1 系统构架

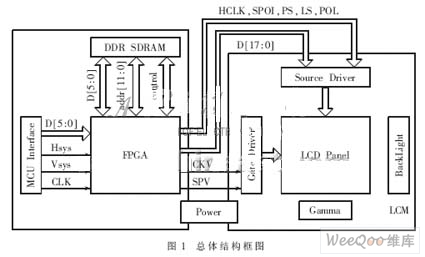

由于DDR SDRAM(83 MHz~167 MHz)和液晶显示器(32.24 MHz~48 MHz)之间的时钟周期不匹配,FPGA在设计中主要起控制协调作用。系统总体构架框如图1, 分为以FPGA为中心的控制模块和液晶显示模块两部分。

FPGA控制模块部分主要负责接收来自单片机的图像数据D[5:0]和控制信号Hsys(行同步信号)、Vsys(场同步信号)和随路传输的输出图像数据的时钟信号CLK(50 MHz以下)。为了节省单片机内部的时钟资源和输出口的数量,对于18 bit彩色显示的LCM,FPGA连接单片机的图像数据输入口可设计为6 bit,再在FPGA内部将接收到的数据串并转换为18 bit数据输出至液晶显示模块。因此在FPGA与单片机接口处,每个时钟FPGA仅接收R、G、B三组颜色数据中的一组D[5:0],经过FPGA的片内RAM缓存满480个D[5:0]以后再存储到一行DDR SDRAM中,同时给出存储单元的地址和各种控制信号。

硬件接口上,由于DDR SDRAM是高速器件,主要考虑与FPGA之间的互连。在布局布线时要求各数据线DQ和数据采样线DQS严格等长,以及采用FPGA对DDR SDRAM的专用接口。

2 FPGA内部模块设计

高实时性是系统设计的基本要求。为统筹兼顾重要性各不相同的任务,一般采用时序和电路结构优化[6],以及各模块并行处理[7]实现。

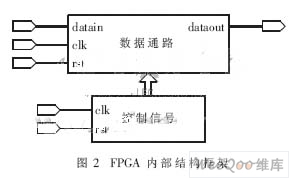

本系统中,3个主要器件都需要FPGA控制,且控制信号较多,数据通路设计又需考虑到3个时钟域的互相转换和相互通信,较为复杂。设计采用了自顶向下的模块化设计思路[8],将数据通路和数据控制通路分离,如图2。单独设计控制信号模块,并输入数据通路模块以控制和处理数据,使输出的数据达到设计要求。

2.1 数据通路设计

数据通路由如图3所示的模块构成。图中未标注的控制信号接口与控制信号模块相连。

PLL(Phase Lock Loop):锁相环是FPGA内部底层资源,此处将输入的50 MHz的时钟通过倍频、移相等得到系统所需的System clk(100 MHz,相位偏移0°)、Write clk(100 MHz,相位偏移-90°)和LCM clk(33 MHz,相位偏移0°)。

DQS:DQS信号控制模块,控制与DDR SDRAM的DQS引脚相连的DQS引脚,双向接口在使能信号oe的控制下产生或接收DQS信号,并将接收到的DQS信号移相90°以后作为FPGA内部对DQ数据组的采样信号。

BUFFER IN:输入缓存模块,在外部时钟和外部控制信号的作用下接收数据并缓存到片内RAM,每满480个数据发出Ready信号,表示缓存中已存满可占用一行DDR SDRAM存储单元的数据。

DQ:DQ数据控制模块,控制与DDR SDRAM的DQ引脚组相连的DQ引脚组,双向接口,在使能信号oe的控制下输出或接收DQ组数据。输出数据时使用Write clock,输入数据时使用DQS模块产生的dqs read信号对输入数据采样,并将结果输出到下级模块。

BUFFER OUT:输出缓存模块,缓存来自DDR SDRAM的数据,并在控制信号的控制下按LCM时序输出彩色图像数据。

2.2 控制模块设计

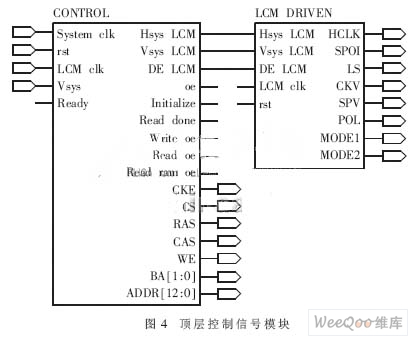

顶层控制信号模块由CONTROL模块和LCM DRIVEN模块两部分构成,如图4所示。主要负责各模块之间的通信,产生控制信号控制数据的流向,向各器件输出控制信号等。

CONTROL:控制模块,为DDR SDRAM分配读、写时间:以200 MHz的数据率在读时间段读出5行DDR SDRAM中的数据,缓存到BUFFER OUT,再以33 MHz的速度读出并输出到LCM;在写时间段探测数据通路中的BUFFER IN中的数据是否缓存完成,若完成则产生信号开始对DDR SDRAM写入数据。在DDR SDRAM的读写过程中根据需要产生DDR SDRAM控制信号、读写行列地址信号,为驱动LCM产生控制信号:行、场同步信号(Hsys LCM、Vsys LCM),数据有效信号(DE LCM)。

LCM DRIVEN:LCM驱动模块,输入LCM的控制信号,产生LCM驱动所需的各种控制信号,并输出到FPGA的I/O,结合外围电路,驱动LCD。

3 实现结果

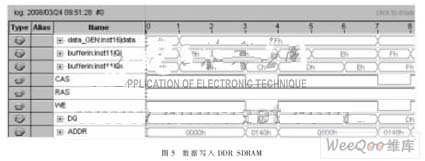

数据接口利用Altera公司专用SignalTapⅡ逻辑分析仪验证。图5、图6是用逻辑分析仪截取的芯片运行时在各引脚或逻辑单元处的实时波形图。图5表示数据输入FPGA直到进入DDR SDRAM的数据通路部分。数据输入经缓冲模块后按照进入FPGA的顺序,分奇偶两路(Qj、Qo)进入DQ接口模块,并合并成一路双倍速经DQ端口输出FPGA。该过程同时输出CAS、RAS、WE等命令信号和地址信号(ADDR)。由于设定了逻辑分析仪以系统时钟100 MHz速率采样各信号,因此对于数据率是200 MHz的DQ双向口,该采样信号只能间隔一个数据采样,而不能完全反映出DQ输出口的数据率。

图6表示数据读出DDR SDRAM进入FPGA经缓冲输出FPGA的数据通路部分。DDR SDRAM在CAS、RAS、WE等命令信号和地址信号(ADDR)控制下,将对应地址存储单元的数据以200 MHz的双倍数据率经DQ双向I/O口输入FPGA,并经DQ接口模块转换为100 MHz的单倍数据率,分两路输出(inst9、inst10)。经输出缓冲模块缓存后,再转换为LCM模块所需的时钟频率33.33 MHz,并行输出FPGA。类似的,由于逻辑分析仪以系统时钟100 MHz速率采样,DQ输入口的数据率在图中不能完全反映出来。

至此,数据经过了设计中所有为其设置的模块和接口,包括输入接口、输入缓冲模块、DQ/DQS接口、输出缓冲模块和输出接口。

设计ARM输出数据时钟是0.3 MHz,随着数据逐渐经片内输入缓存输入DDR SDRAM替换掉原有数据,对应在屏上的图像也逐渐被替换,该验证过程说明DDR SDRAM在过程中起到了帧存储器的作用,设计的系统与预期要求相符。

该显卡系统以单片DDR SDRAM为显示存储器存储图像数据,以FPGA为控制中心,嵌入式系统仅需通过I/O口在需改变图像时输出一帧数据至显卡,不需实时提供数据流和各种显示器控制信号,从而使嵌入式微处理器有足够的时间控制其所在的自动化系统。

设计采用800×480分辨率液晶显示器为图像输出设备,具有面向微处理器的通用接口,可匹配数据输出时钟频率50 MHz以下的微处理器。由于系统图像数据来自单片机,因此分立的系统没有数据来源,为了验证设计的正确性,验证步骤里采用了周立功单片机有限公司的EasyARM2131开发板验证设计结果。验证结果表明,设计达到了预期要求。(电子技术应用 作者:何汶静 黄子强)

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。