越来越多的消费应用开始在设计中集成流式视频,结果引入了许多标准和专有的加密算法。但是加密方案以及实现方法不统一导致视频接收设备在设计和支持方面存在巨大的挑战。DeviceDNA作为FPGA的一项新功能,可保证视频接收机的设计安全,同时还可为测试和验证流程提供支持,从而提供成本经济的高质量安全解决方案,支持多种不同的视频流加密协议。

视频越来越多地应用在我们生活中,除了在电视上的应用,还被应用在计算机、汽车、PDA/PMP、iPod和手机上。现在,甚至冰箱上可能也应用视频!

消费者希望能够随时随地享有视频所带来的便利,但是如此广泛的视频需求产生了大量不同的流式视频压缩标准,以满足对不同屏幕尺寸分辨率以及高带宽的要求。

要为这么多不同种类的设备提供视频内容支持,因此在传统有线电视和卫星供应商之外又诞生了许多新的视频流提供源(以及相应的厂商)。电话线、因特网和无线通信,在支持流式视频发展的同时也为流式视频带来了明显的安全问题。为了解决这一问题,不同的流式视频源引入并采用了越来越多的标准和专有加密算法。然而,不同厂商间加密方案以及实现方法不统一导致视频接收设备在设计和支持方面存在巨大的挑战。

FPGA提供灵活的解决方案

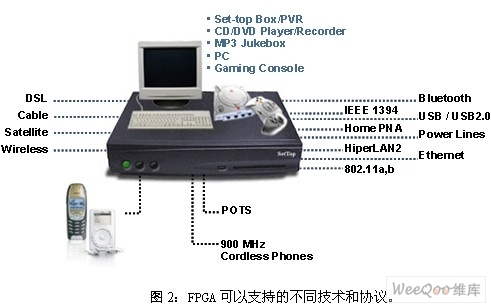

多年来,低成本FPGA器件已经成为机顶盒和视频网关的关键器件,可提供视频增强、丢失像素替换、视频转换、产品灵活性以及产品差异等功能。此外,这些器件还允许生产商方便地支持不同的技术和协议,如图2所示。

FPGA平台的传统灵活性以及专用的算法功能是解决多种不断变化的标准和专有加密算法的理想解决方案。器件重配置能力可以根据需要方便地改变解密算法。通过FPGA器件重配置,设计可利用更少的逻辑门和更少的器件,从而以更低的总体成本支持更多算法。现场可升级能力能够快速方便地应对新算法和算法变化,因此可保证产品是未来适用的(future-proofing),并且不必进行昂贵的现场更换即可延长现有产品的寿命。

硬件安全问题

视频源提供商的担心已经不仅局限于视频流本身的安全性,而是已经扩展到接收硬件的安全性。有些视频源提供商正在设法将其许可和视频流限定范围定为能够提供安全视频接收机的系统。这需要很多企业寻求减少支持的数量并提高器件级的安全性,以进一步提高总体设计的安全水平。可编程逻辑器件生产商赛灵思公司提供的FPGA平台则可解决这一问题。该平台的DeviceDNA技术可提供支持多种解密算法的能力和更高的器件级安全性。

DeviceDNA允许设备生产商将一个的非易失工厂序列号直接写入到FPGA器件中。每个器件的ID都不同,因此可以将设计绑定到特定的FPGA器件中。DeviceDNA可以作为接收设备的独特序列号,一个的许可代码,或者与用户定义的写在FPGA构造中的算法配合使用,从而将特定的设计与特定FPGA器件紧密绑定在一起。如果某些人试图克隆或拷贝过的设计,或者将位流写入另一片不同的FPGA器件,那么由于器件的ID号码变化,设计就不会通过。DeviceDNA是一个57位长的序列号,可以通过器件内部的逻辑构造读取。

DeviceDNA与用户定义算法紧密结合能够以合理的系统成本实现所需要的安全度。在采用算法的方法中,安全性的关键是算法本身。在本方法中,安全过程中必须有某些部分要保密,在本中则是用户定义的算法本身。由于算法在PPGA逻辑构造中实现,因此成为FPGA数百万配置位中的少数位。除非知道这些位如何组合在一起,或者知道算法本身,否则参于任何试图拷贝设计的人来说,看起来都仅仅是一堆数字。

用户定义的算法可以如系统所需要的一样简单或复杂 - 例如:可以是简单的哈希算法,或者更为复杂的三次DES、AES6?、128或256位,甚至是完全定制的算法。同时还可以将用户定义的算法集成到接收器的流程内部。这样可以进一步将接收单元与视频流系统、设计与特定的接收单元捆绑在一起,从而进一步提高抵抗克隆的安力。此外,算法可以改变以支持不同的视频解密协议配置,甚至在不同型号或不同代产品间采用不同的算法,从而进一步保证安全性。

安全性提高对生产的影响

硬件安全性问题同样适用于生产流程,特别是板级测试和验证。因此,设计中经常将JTAG功能移除,因为JTAG功能易使设计导致反向工程。许多企业都采用JTAG来缩短测试时间并提高测量和验证流程中的系统测试覆盖范围。然而,没有JTAG,就需要更多的测试,特别是系统级测试来保证一定的测试覆盖范围。不使用JTAG技术会提高生产成本,并终影响到系统总成本。

JTAG的问题在于INTEST命令,用于检查设计的内部逻辑功能。反向工程时,这一命令可用来判断设计的功能。图3给出了一个简单的例子,其中数据移入寄存器,执行INTEST命令,这样数据会在时钟作用下移入逻辑构造,进入下一寄存器,结果可以被读出。由于可将总体设计的复杂度缩小到更小的逻辑模块,因此这一命令可使反向工程的工作更容易。

一些FPGA平台可帮助防止发生这一过程,同时仍然允许生产商完成其管脚至管脚(pin-to-pin)功能。例如,在Xilinx? Spartan?-3A 平台中, 可在设计中使用BSCAN_SPARTAN3A宏模块,其检测逻辑可监控FPGA构造中的JTAG控制信号,如图4所示。如果检测到JTAG控制信号的活动,用户在设计可以立即绕过关键逻辑或关断关键功能,不再执行正确的功能。这样反向工程人员读到的将是不正确的功能模块,在不能完成预期功能的解决方案上浪费时间和资源。

支持DeviceDNA的FPGA平台可保证视频接收机的设计安全,同时还可为测试和验证流程提供支持,从而能够提供成本经济的高质量安全解决方案,支持多种不同的视频流加密协议。欲了解更多DeviceDNA或JTAG的详细信息,请登陆www.xilinx.com/cn参考《Spartan-3系列配置用户手册》。(Mark Moran,通用产品部战略营销经理, 赛灵思)

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。