概要

常见的多级低通有源滤波器的增益排序方法是把大部分乃至全部增益放在级。如果只考虑要降低低频的输入参考噪声,这是正确的设计方法。然而,其它的几种考虑因素可能会使您改变这种增益排序,以实现更为出色的实施方案。这些需要考虑因素包括:每级特征频率范围内的噪声峰值效应、高 Q 值高增益级的过冲导致压摆范围受限和/或削波、可靠实施所需的放大器带宽。本文将对上述情况进行描述,为其找出相应实施方案,并对这些方案的效果进行详解。

多级低通有源滤波器的设计考虑因素

每个多级有源滤波器设计人员都不得不为各级 Q 值的排序和每级该分配多少增益之间的折衷而大伤脑筋。如果滤波器的总增益要大于 1,简单的设计方法就是把大部分乃至全部的增益放在级。经过正确分析得出这种方法可以实现输入参考点噪声(当噪声频率远低于滤波器特性频率时)。另外,对于标准的多极点设计,需要从低到高布置一系列的 Q 值。在哪里布置 Q 值的是一个非常重要的考虑因素,实际上也是实施方案成功与否的关键。这些 Q 值的会出现的输出噪声峰值,也是有可能导致压摆范围受限和/或者削波的阶跃响应过冲的地方。许多设计工具把这放在前面,这恰与将大多数增益放在级的目标相冲突。有些设计工具则把大多数增益放在,结果导致噪声峰值远远超过必要水平,增大了滤波器输出的整体噪声。某些设计工具则采用折中方法,把 Q 值的放在中间(针对 4 阶以上而言),这种方法似乎非常适用于某些应用。

在采用有自身性能限制的真实部件来真正构建这些滤波器时,上述的考虑就不再是纸上谈兵。使用一种近期开发的在线设计工具(参考资料 1),可以开发出多种能够实现相同目标频率响应的。在选择不同的增益和 Q 值排序的情况下,它们的阶跃响应、噪声以及要求的放大器性能裕量会大相径庭。

当然,只有在设计的低频通带总增益大于 1 的情况下才需要考虑增益排序。尽管增益和 Q 值排序问题也适用于多级反馈 (MFB) 或无穷大增益拓扑,这里将使用 Sallen Key 滤波器 (SKF) 来说明问题和结果。有资料显示特定 SKF 级实现的增益是受限的(参考资料 2)。这只在阻容解决方案受到某些其它限制时才会出现。一般假设需要等电容设计,实际上这将限制每级可实现的增益。然而,对于板级实施方案来说,等电容假设是人为的,可能对于针对集成的设计流程更有用处。这里的设计不局限于等阻或是等容,让设计可以实现通带内任何需要的增益。不过,需要注意的是,随着增益的增加,这会加剧滤波器对组件变化和增益变化的灵敏度。增益的增加要求该级用于设置滤波器和增益的阻容元件具有更小的阻容容差。当然现在已经可以提供这样的元件。

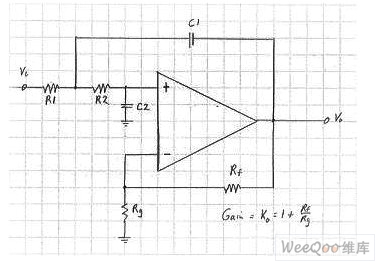

参考资料 1 的设计流程倾向于增大电阻,让电阻产生的噪声与运算放大器固有噪声相比可忽略不计。同时设置 1/R2C2 极点,使之降低滤波器级的内部噪声增益峰值(图 1)

图1. 基本的 SKF 二阶低通滤波器

在各级增益分配中对要求的运算放大器带宽的考虑

图 1 所示的设计要成功实施,必须估算出的放大器闭环带宽。通常,如果要求放大器带宽乘数是目标 Fo 的 100 倍到 200 倍,就比较容易实现。更为复杂的设计会根据该级增益和目标 Q 值来计算目标带宽,从而得到放大器带宽随 Fo 和 Q 值变化而变化的理想灵敏度。

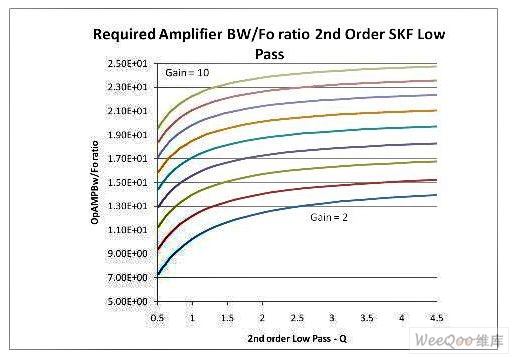

带宽乘数计算随 Q 值变化(在给定增益下)的示例见图 2。该图显示的是图 1 电路的放大器带宽与 Fo 之比,其目的是提供恰好足够的放大器带宽,实现高的滤波器实施方案,从而在带宽变化为 15% 的情况下,Fo 变化不超过 2%(参考资料 3)。使用带宽裕量高于本设计的放大器当然是可以的,不过本设计的目的是降低成功设计的门槛。

图 2. 所需的运算放大器带宽与增益和 Q 值的关系

要注意的是,本图重点强调带宽。这样可以使用电流反馈放大器 (CFA) 或电压反馈放大器 (VFA) 器件来实现 SKF 拓扑。CFA 器件在一定的增益范围内,能够保持恒定的闭环带宽,故特别适合用于实现高增益。本图(根据参考资料 1 的算法得出)在这个方面表现得特别明显。举例来说,在增益为 2,Q 值为 0.5 的情况下,它只需要 7 倍的带宽裕量。在 25 倍带宽裕量下,增益可以达到10,Q 值达到 4.5。这些相对适度的设计裕量允许使用更多种类的物理器件来实现特定的滤波器标准,但需要使用某些支持该带宽的可以调整组件的算法,才能达成滤波器的设计标准。采用理想等式来计算阻容值的设计流程需要放大器带宽具有更大的裕量。

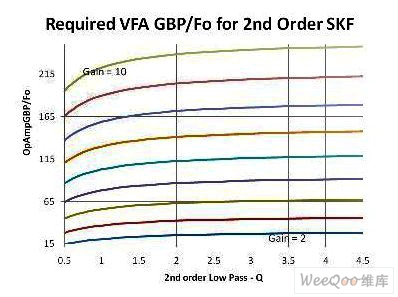

若使用 VFA 器件,需要进行如下修正:将每个数据点与增益相乘,得到所需的增益带宽积与 Fo 的比例。如图 3所示,所有的曲线都上移并展开。

图 3. 给定增益条件下所需的带宽增益积与 Q 值参数

这里我们可以开始研究使用 VFA 器件构建的简单二阶 SKF 实现更高 Q 值和更高放大级增益所需的某些极端乘数。举例来说,如果增益为 10、Q 值为 1,本曲线说明我们需要增益带宽积至少为 215xFo 的放大器。在 Fo 为 1KHz 时,这个要求并不难实现。但是如果 Fo 大于 1MHz,就会比较困难。这就是为什么具有级增益的更高速 SKF 倾向于使用 CFA 运算放大器的原因。

设计一款实用、分立式运算放大器的多级有源滤波器要求每的带宽只要满足本级的需要即可。一般来说,过大的带宽裕量是有代价的,或会增加功耗,或会增加购买成本。此外,在各级的带宽和压摆率要求能够保持在大致相当的范围内的条件下,还可以使用由统一基础放大器型号构成的多通道器件来实现多级滤波器。在理想条件下,可以通过在图 2 或者图 3 上画一条水平线来获得完全相同的带宽要求,然后使用水平线与参数曲线的交叉点来设置每的增益和 Q 值。然而,由此引申的更加直观的解读足以满足我们的需要。这些曲线明确地说明,随着 Q 值或者 Fo 的增加,该级分配的增益应该减少。除了Butterworth 滤波器的每Fo 值都相等,其他滤波器在大于三阶的情况下,每级的 Fo 都会发生变化。多数典型的低通滤波器的形态是 Fo随 Q 值增大。这使所需放大器的带宽受到的影响大于 图2和图3中显示的Q 值相关性的影响(如图 2 和图 3 所示),但这种影响很大程度上要取决于所选择的特定滤波器的形状。

下面将举例说明这种影响。以一个六阶、0.5 度等纹波相位低通滤波器为例。该滤波器 Fcutoff 为200KHz,总体增益为 10。我们首先采用增益逐级递增, Q 值逐级递减的方法,然后采用反向操作,增益逐级递减的方法,然后将每种方法估算的放大器带宽和增益带宽积记录在表格里。后者对是否只能对这些级采用 VFA 非常重要。该滤波器形状在输出端具有非常出色的低过冲阶跃响应,但在滤波器内部各级会产生一定程度的振铃和过冲现象。

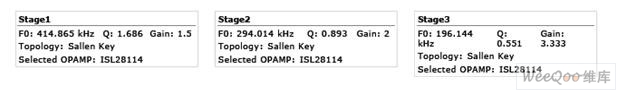

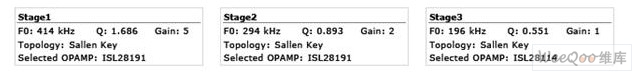

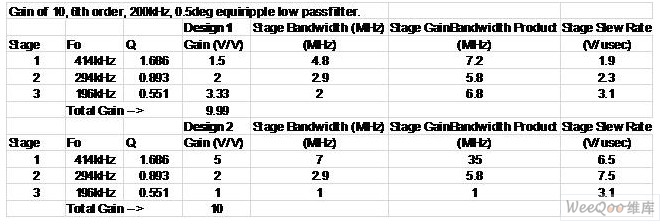

图 4 所示的设计按照参考资料 1 的思路,共分为三级。Q 值的放在级,增益;中间 Q 值略低,增益略比级大; Q 值,增益。可见从左到右 Fo 逐渐减小,增益逐渐变大。

图 4. 此增益和 Q 值分配更为接近带宽和压摆率要求

另外,我们也可以采用更为常见的方式来设计,将级的增益设置为,逐级递减。一般来说,这样可以提供更低的输入参考噪声。这对低频率来说是可行的,但不会像想象的那样对整体输出噪声产生太大影响。图 5 所示为同样的滤波器标准,三级增益分别按 5、2、1 排序,实现了相同的整体滤波器形态。同时 Q 值和 Fo 排序从输入到输出也呈现出由高到低的态势。

图 5. 使用更常见的设计流程的增益和 Q 值分配

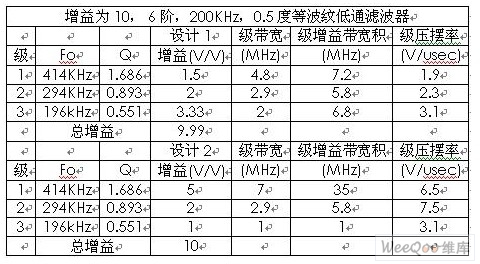

使用生成上面曲线的算法,我们可以把估算的放大器带宽乘以该级增益,得到每所需的增益带宽积,并制成表格。虽然这种算法只在参考资料 1 中有所提及,但大多数设计工具有类似的 通过Fo、Q 值和增益得到所需的放大器带宽的计算,因此得出的结果也是类似的。我们还可以计算出每所需的压摆率峰值。具体计算将在后文介绍。我们这里的目标是实现 4Vpp 的终输出摆幅,通过综合每输出的标称摆幅和 Q 值较的过冲阶跃响应导致的 增大了的dV/dT 峰值,我们可以估算出所需的压摆率峰值。

上述表中文字

图6. 所需的增益带宽积和压摆率的比较

每种方法对带宽的要求体现出值得注意的差异。很明显第二种方法要求的带宽增益积变化较大(35:1,而种方法的带宽增益积基本是恒定的)。此外,由于现在头两级要求较高的压摆率,与种设计相比,参考资料 1 提出的设计流程需要在头两级采用速度较高的器件(图 5),(ISL28191 的 GBP 是 61MHz,ISL28114 的 GBP 是 7.7MHz)。的压摆率保持不变,但前面两级现在要求更高的压摆率。终的输出总是在固定的目标输出步长和滤波器整体形态下达到相同的压摆率,不过种设计在前两级要求较低的峰值压摆率,这在每都使用同样的放大器的情况下,是更加受欢迎的。

虽然可能找到某种“优化”算法来实现准确的增益分配,以得到固定的增益带宽标准,但以本文所述的大略的方法来分配增益可以便于归集所需的放大器带宽。出于多种原因,在滤波器级数超过的情况下,高 Q 值的级增益应保持较低,而如果需要更为一致、适中的放大器带宽标准,应更多地将总增益分配到较低Q 值的级上。这样还会得到较低的 Q 值随 Ko 变化的灵敏度。

但是如果把设计 1 中的 Q 值从输入到输出由高到低排序会怎么样呢?这样确实看起来更能保持各级所需压摆率的一致性,另外还可以在削波和整体噪声方面体现出优势。

二阶阶跃响应所需的压摆率峰值计算

多级有源滤波器的每都会产生输出电压转换,这就要求限制 dV/dT。在这个由阶跃响应主导的例子中,如果该 dV/dT 超过了选定的运算放大器的额定压摆率,阶跃响应通常会大幅偏离预期值。因此,在谨慎的增益和 Q 值排序方法中,我们需要考虑内部和输出级对 dV/dt 峰值的隐含要求。频域主导的应用会对每输出都有隐含的压摆率要求。在这种情况下,以总体响应的 SFDR来作为 标准会更加有意义,但这方面的讨论已经超出了本文的范围,不过可以得出与本例使用的阶跃响应主导的分析类似的结论。

虽然多级有源滤波器内部实际的波形在时域上可以非常复杂,但可以采用合理的保守方法,把每当成受到了理想的输入阶跃激励来分析。任何真实的滤波器产生的级间输入的边缘速率都会低于理想阶跃,这样就给我们一些设计裕量,并允许使用较为简单的等式。

如果我们假定任一二阶低通滤波器级受到理想输入阶跃激励后会产生 Vopp 的目标摆幅,我们就可以通过分析输出时间波形得出 dV/dt 峰值。有意思的是,其结果在文献中很难找到,不过从参考资料 4(等式 55),我们可以得到一个简单的近似等式,如等式 1 所示。

等式 1

等式 1

如果我们知道理想的输出端完整步长以及第二级的 F-3db,这个近似等式可以帮助我们很方便地得出 dV/dt 峰值。我们可以通过下面的式子从目标滤波器极点得到F-3dB

等式 2

等式 2

根据设计 1 和设计 2 所举的例子,每 F-3db 的值计算如表 1 所示。(记住我们保持 Q 值和 Fo 排序不变,只是简单地分配了不同的增益,使滤波器内部的阶跃幅度不同)

表 1.

那么我们再来观察 Q 值的,这通常也有的 Fo,也就是的带宽。如果我们能够推测出固定的输出 Vpp 标准,就可以让等式 1 的结果落在更小的范围内。简单的方法是随 F-3db 带宽的增加,降低所需的 Vstep。设计 1 实际上就是通过在输入级使用更低的增益做到了这一点。而设计 2 显示了没有降低较高 Q 值级(图 6)所需的 Vstep 得到的压摆率结果(如图 6 所示)。图 6 显示的设计 1 和设计 2 的压摆率是以 4Vpp 的终输出目标摆幅为条件得出的。具体是使用等式 1 计算出该输出条件下的压摆率(使用 2 倍乘数以得到额外裕量),然后用该级标称摆幅除以该级标称增益得出由前进入的步长,使用该摆幅和该级的 F-3db 计算所需的压摆率,依次类推回级。

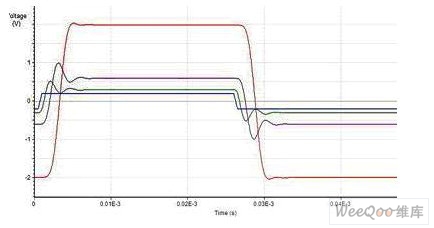

每个 Q 值较高的级都会在阶跃响应中产生相当大的过冲。设计 1 通过让有较高过冲的级的摆幅较低,并从输入到输出逐步增大阶跃摆幅来避免削波。设计 1 的阶跃响应仿真运行结果(参考资料 1)得出的阶跃响应如图 7 所示。该图展示了通过滤波器每的输入和输出电压。注意摆幅的逐渐增大和终输出级极低的过冲。这是这种类型滤波器形态的典型特征。其在 +/-2.5V 双极电源下产生 +/-2V 双极性摆幅。

图 7. 设计 1 的阶跃响应仿真

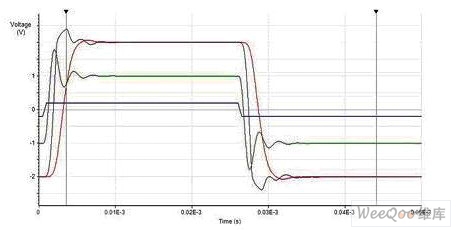

相比之下,设计 2 的阶跃响应在级间出现了削波,导致非常不理想的仿真响应结果。这是因为级的增益较大导致设计中较早出现了大摆幅。如图 8 所示,仿真中宏模型正确的预计到第二级的输出会出现削波,而将其干净地滤除了。

图 8. 设计 2 的阶跃响应出现削波

这明显比设计 1 的效果差。虽然这是个有些极端的例子,但这也确实说明了用增益来降低级间削波风险的重要意义。

多级滤波器 Q 值排序对噪声增益峰值的考虑

对曾经测量过 SKF 滤波器输出噪声频谱的人来说,都会有些惊讶地发现噪音峰值有多么高。SKF 滤波器的一项不为人注意的特性是其高峰值噪声增益在某种程度上可以通过认真选择电阻值来减轻。

运算放大器线路的“噪声增益”指输出电压的分压比与差分输入电压比值的倒数。这也给出了运算放大器自身的输入噪声电压到输出端的增益的频率响应。同样它还是运算放大器开环增益与该噪声增益的比,即 SKF 滤波器内部通带频率上的环路增益。这是极为有用的因子,它说明环路增益越大,谐波失真越低。因此,出于多种原因考虑,应了解并尽力降低 SKF 的噪声增益峰值。

等式 3 所示的是图 1 二阶低通 SKF 滤波器的噪声增益拉普拉斯传递函数的基本形式。分子是一个二次多项式,实数零点分布在较宽的范围内(一个小于 ω0,一个大于 ω0),而分母的极点是滤波器需要的极点。这个分母的表达式实际上是导入增益元件前的无源2 R和2 C电路的极点等式(将图 1 中的放大器从电路中去除,让 C2 接地,就可以得到 C2 之上的从输入到输出端的传递函数,而这个表达式的极点就是 SKF 噪声增益表达式的分母)。

等式 3 噪声增益à

分母等式与所需的滤波器响应一致。如果我们在分母的线性系数中用 Ko/R2C2 项来做替代,然后按滤波器指标项重写等式,我们会发现实际上我们在噪声增益响应方面没有多少裕量。

等式4 滤波器指标项的噪声增益à

除 1/R2C2 极点外,该等式中的每一项都已经被所需的滤波器形态、DC 增益以及 Ko 决定了。这种现象在某种程度上可以用来降低噪声增益峰值,但噪声增益峰值主要还是受控于所需的滤波器 Q 值。简单地说,让 SKF 滤波器的 R1/R2 值大致处于 0.15 至 0.7 之间。使该比例尽量接近 0 从数学上来说是准确无误的,这样可以减少噪声增益峰值,但 R1 为 0 又会带来其它问题。

所以噪声增益在频率范围内始于 Ko,终于 Ko。在 ω0 附近,由于极点等式反映的所需的滤波器形态(Q >.707 会在所需的频率响应内形成峰值)和低于 ω0 时形成的零点造成的峰值,因此会有较大峰值出现。一个显然的问题是运算放大器环路内的噪声增益峰值是否会影响稳定。在峰值位于放大器开环响应范围内的时候会影响稳定。不过,即便在图 1 和图 2 所示的极低带宽裕量条件下,噪声增益曲线与开环增益的交点也会远高于下面所示的峰值。但是这个问题说明了不要采用太大的放大器带宽与 Fo 乘数。理论上讲,可以使用几乎任何放大器带宽,通过迭代,得到所需滤波器形态要求的电阻值和电容值。不过让放大器带宽与 Fo 的比值过大就会引起局部环路稳定问题。

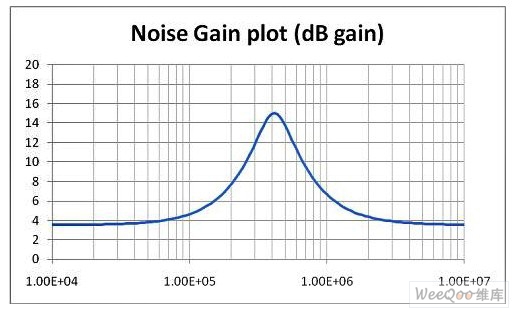

图 9 所举示例显示的是设计 1 级的噪声增益幅度。它采用参考资料 1 的设计算法,首先控制 R1+R2 的值使加在运算放大器自身的噪声近乎可以忽略,然后在上面建议的范围内设置 R1/R2 比例。

图 9. 设计 1 级的噪声增益幅度

这里的初始增益是 1.5V/V,终的噪声增益是 3.56dB。在 414KHz 的 Fo 频率附近,我们发现了峰值惊人,增益增加了近 11.4dB,高达 15dB,是滤波器所需增益的 3.7 倍。这所需的滤波器形态只体现出了从 3.56dB 的DC 增益到 增益8.44dB 的峰值,远远低于隐藏于该响应中的噪声增益峰值。如果该较高 Q 值级还能提供更多滤波器总增益,整个曲线将会上移。这将在后面演示。

谨慎起见,应该在该超高噪声峰值之后安排 Q 值更低、Fo 更低的级。这样可以过滤这些峰值,实现较低的整体输出噪声。

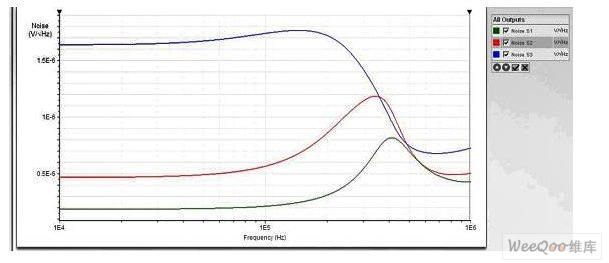

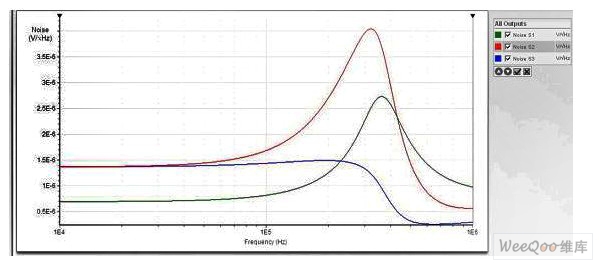

图 10 显示的是设计 1 滤波器每的输出噪声。它包含了根据参考资料 1 生成的设计的全部参数、噪声电压、噪声电流以及电阻噪声。前两级的输出有明显的噪声峰值,但终输出噪声峰值近乎可以忽略,因为的 Q 值较小。这里的噪声峰值在 190KHz 时为 1.76?V/√Hz。

图 10. 设计 1 的输出噪声图

让我们回到设计 2,采用 ISL28113 来完成设计,根据下面的噪声图(设计中经设置电阻后会以运算放大器噪声电压为主,故该图主要体现的是运算放大器的电压噪声效果)进行输出噪声的公平比较。该图显示前两级都出现了明显的噪声峰值,但由于 Fo 和 Q 值相对较低,起到了良好的滤除作用。该图显示 200KHz 时噪声峰值为 1.49?V/√Hz,略低于设计 1。

图 11. 设计 2 的输出噪声

因此,在这种情况下,把增益更多地放在级确实可以轻微降低总输出噪声。但一定要把Q 值的布置在,这一点是非常重要的。把 Q 值的级放在后面的设计会导致的整体噪声。即便该级的 DC 增益只有 1,其较高的频率峰值也会形成不理想的整体噪声结果。

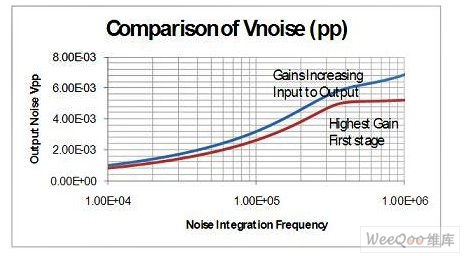

有兴趣的话,还可以计算出两个设计的输出噪声 Vpp。计算的方法是将频率范围内的输出噪声功率相加得到(Vrms)2,然后开方,将平方根乘以 6 就得到大致的噪声 Vpp。图12显示的是如果两个滤波器后接截止频率在x轴上的矩形噪声滤波器的情况下估算测得的输出噪声Vpp。

图 12. 设计 1 与设计 2 的综合输出噪声电压比较

举例来说,我们在 200KHz 六阶设计后接一个 500KHz 的矩形滤波器,我们可以在设计 2 上测得大约 5mVPP,在设计 1 上测得 6mVPP。总体来说,这点差异不会给设计 1 前边提到的优势在噪声方面造成太大影响。

所以在这种情况下,将增益更多地排布到级可以带来某些噪声方面的优势。但这里的想法是建议把 Q 值适中、增益适中的级放在级,随后是 Q 值、增益较低的级,是 Q 值、增益较高的级。如参考资料 1 所提供的自动设计算法,把 Q 值从高到低排序,把增益从低到高排序,可以在放大器带宽、压摆率一致性、阶跃响应过冲以及削波性能方面实现优异的特性,只是在某些情况下输出噪声有适度的增加。

结论

如果多级低通有源滤波器的目标之一是在每级使用相同的放大器的同时,降低对运算放大器的设计裕量要求,那么给 Q 值较高的级分配更低的增益是非常合理的选择。为避免终输出出现噪声峰值,把 Q 值的级放在。为限制级间削波,在滤波器总增益大于 1的情况下,该低Q 值级应具有一定的增益(尽可能大于 2)。增加级的增益可以略微减少输出噪声,而将具有低增益的 Q 值级放在中间可以略微改善噪声特性。

[1]. CFA datasheet https://www.dzsc.com/datasheet/CFA+_2327767.html.

[2]. ISL28191 datasheet https://www.dzsc.com/datasheet/ISL28191+_1721825.html.

[3]. ISL28114 datasheet https://www.dzsc.com/datasheet/ISL28114+_2025453.html.

[4]. ISL28113 datasheet https://www.dzsc.com/datasheet/ISL28113+_2025452.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。