摘要:为了解决采用DSP技术的雷达模拟器的硬件外围电路设计复杂、人机交互界面设计繁琐的问题,利用FPGA芯片控制能力强,设计灵活以及LabVIEW语言易于实现人机交互界面设计等优点,采用计算机结合NI公司的PCI-564OR数据收发中频卡,设计了雷达回波模拟器。利月Matlab仿真出线性调频、杂波、干扰等信号数据后,通过PCI总线把它们写入板卡的FPGA中,由FPGA控制时序,经 D/A 转换后将数据送出,从而实现雷达回波信号的模拟。实验结果表明,该模拟器具有良好的通用性和度,并且结构简单,使用灵活。该设计形式对于今后雷达信号模拟器模块化设计具有借鉴意义。

引言

现如今,为雷达检测提供回波模拟信号的雷达回波模拟器层出不穷,而绝大多数模拟器采用微型计计算机+数字信号处理器件(DSP)+数模转换(D/A) 的方式。这种方法存在两个缺点,一是由于DSP的控制力不强,且其外围的电路设计比较复杂;二是这种设计在软件实现上是以C语言为主,而用C语言编辑人机交互界面,费时费力。然而倘若采用微型计算机+可编程逻辑器件(FPGA)+数模转换(DA),则可避免上述问题,因此通过计算机配合 NI公司的PCl-5640R数据收发中频卡产生雷达中频回渡信号,在这一设计中板卡所带的FPGA 芯片,具有很强的控制能力,设计较灵活;同时,该板卡可以用LabVIEW 编程实现功能,这种图形化语言易学易用,而且有丰富的图形件,易于实现人机交互界面设计,可以很好地解决上面两个难题。

1 系统设计

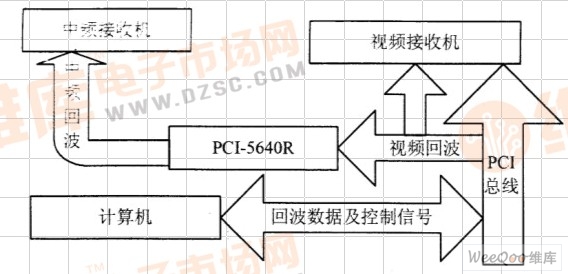

该模拟器主要曲计算机和PCI-564OR数据收发中频卡组成,其组成框图如图1所示。

图1 系统组戚框图

计算机负责通过LabVIEW等语言,对板卡的FPGA芯片编程,并通过驱动程序驱动PCl-5640R王作。

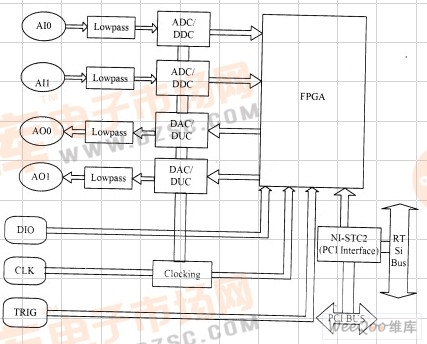

PCl-5640R数据收发中频卡主要由PCI总线接口、FPGA、数字上变频芯片AD9857、数字下变频芯片AD6*、存储器以及触发电路组成。FPGA型号为Xilinx Virtex-5 SX95T,有640个乘法器,它不需要通过Maxplus Ⅱ编程,而直接用LabVIEW编程再编译即可;AD9857有两路14 的高性能DAC,内部时钟达200 MHz,内置数字上变频器,单端输出, 阻抗50Ω;AD6*有两路l4位高性能ADC,内部时钟达100 MHz,内置数字下变频器,单端输人,阻抗50Ω。

中频卡在该系统中的主要作用是完成模拟中频信号的输出。它可以将主板计算出的视频回波数据通过高速D/A芯片转换为模拟的视频信号,也可以利用板卡上的FPGA将田波数据存储,再经AD9857将信号正交混频到中频后经D/A转换输出中频回波。其原理框图如图2所示。

图2 中频卡原理图

2 功能实现

2.1 功能说明

PCI-564OR中频卡能够通过LabVIEW编程来实现其功能,而且支持其他语言程序的调用,如C,VC,LabWindows CVI 等,同时能结合 Matlab仿真技术计算出雷达回波信号及杂波等数据,将 Matlab 模拟产生的回波数据到PCI总线传输至FPGA中,FPGA对高速的数据流进行缓冲、分离,送入存储器存储,并按照数字上变频芯片的时序送出对应的数据,产生数字上变频芯片正常工作时所需的控制信号。数字上变频芯片AD9857将视频回波数据转换为中频回波数据进行模拟输出。

该模拟器把Matlab仿真好的回波信号先进行存储.然后不断地循环输出。在要求数据传输速率和存储空间大小的同时,要求该模拟器必须能够连续不断地提供回波数据,不能出现间断,工作要稳定可靠。

2.2 PCl-5640R程序设计

2.2.1 设计思想

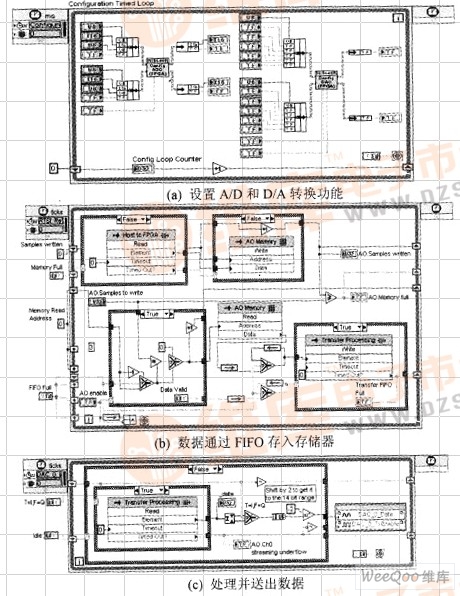

总的程序分圭程序设计和FPGA程序设计两块,主程序负责将数据读取、转换,然后送入FPGA,FPGA程序负责在FPGA上设计存储器,存储数据,并将数括通过 D/A转换送出。将Matlab仿真的数据以文本艾件的形式存储,并通过LabVIEW中的路径控件将文件载入,读取数据,再通过LabVIEW编程将数据转换为适合送入PCl-5640R中频板中的FPGA模块,并经过上变频器AD9857输出的数据,进而送人FPGA中。由FPGA控制将数据送入AD9857,终输出中频回波信号。软件设计分主程序设计和FPGA 程序设计,结构图分别如图3,图4所示。

图3 主程序结构图

图4 FPGA程序结构图

图4中的三个模块分别是三个定时循环,它们在执行时并无先后顺序,各自按预定的时序循环。

2.2.2 程序设计

(1)主程序设计

主程序的设计思路是:首先启动 PCl-5640R板卡,然后调用仿真数据进行转换,再将数据送入FPGA程序中处理,并不间断地从FPGA读取数据,以监控是否有溢出,判断是否有错误,若有则中断程序,如无则继续监控是否有溢出和有无错误,程序如图5所示。

图5(a)是将仿真数据通过路径控件读入到主程序中,再转换为16位数,然后通过Host to FPGA. Write控件将数据送入FPGA程序中。图5(b)是先通过一个逻辑控件开始一个FPGA程序中的Case结构,该结构是用于数据读取,然后通过一个for循环监视Memory是否溢出和数据是否送出到AO0口,并判断是否停止,结束数据读取并使FPGA停止工作。

(2)FPGA程序设计

FPGA程序分为两块,一是在FPGA上设置A/D和D/A转换功能;二是在FPGA上加存储器,将数据通过FIFO存入存储器Memory ,再通过FIFO将数据送入设置好的AO0口,进而将数据送出。FPGA程序设计如图6所示。

图5 主程序设计

图6 FPGA程序设计

图6(a)中的Nl5640R Config ADC和NI5640R Config DAC是用于在FPGA芯片上设置A/D和D/A转换功能的程序模块,这两个模块是PCl-5640R特有的,只需对其参数遴行配置即可。图6(b)中数据是通过FIFO送入Memory中,再通过计算Memory 的地址,寻址读取数据,再送到Transfer Processing这个FIFO中。图6(c)是将数据从这个FIFO中读取,再转换成 14位数送入AO0口。

2.3实验结果

实验以生成较具代表性的单载频矩形脉冲信号、线性调频信号并添加杂波信号来检验模拟器的信号生成功能。

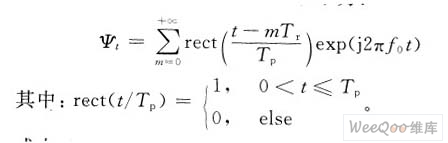

(1 )单载频矩形脉冲信号

单载频矩形脉冲信号是一种载频为fo,脉冲宽度为TP的脉冲调制正弦信号,可表示为:

式中:Tr为脉冲重复周期;rect ( t/Tp,)为信号的归一化复包络。

(2)线性调频信号

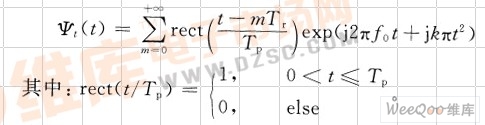

线性调频信号可表示为:

式中:fo为中心频率;Tp,为脉冲宽度,Tr为脉冲重复周期;k=S/Tp为调频斜率;B为线性调频信号的带宽。

(3)杂波信号

这里模拟的是瑞利杂波,其幅度概率分布为瑞利分布,功率谱为高斯谱。

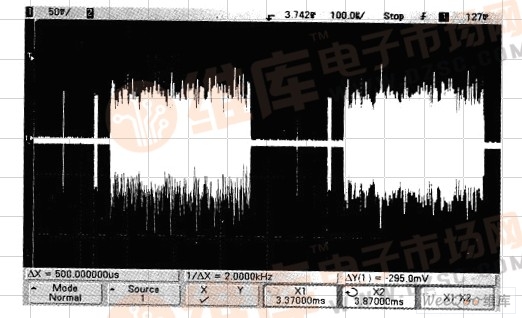

将以上数据叠加,得到混合波形数据。将混合波形数据通过 LabVIEW程序送到PCl-5610R中频卡。输出的波形如图7所示。

图7 混合波形图

混合波周期为500 uS,载波频率为65MHz,依次由脉宽为0.3 us的单载频脉冲,脉宽为6 uS的线性调频信号和所占时宽300 us的瑞利杂波组戚。

3结语

实验结果表明,用计算机结合NI 公司的PCI-5 640 R中频卡,配合Matlab仿真软件,能够根据需要产生较逼真的雷达模拟回波。该模拟器具有灵活性和稳定性的特点,可以根据需要产生信号、嗓声、杂波和干扰等;同时,由于板卡能够通过LabVIEW语言对卡内的FPGA编程来实现其功能,在修改参数重新对FPGA进行配置时,只需完成对应的软件编译,节省了芯片再配置的时间,而且LabVIEW丰富的图形控件为人机交互界面的设计与扩展节省了时间。本文旨在探萦模拟雷达回波信号的新途径,在信号的实时性方面尚未实现,由于FPGA可以以完全并行的方式进行运算,能够在一个时钟周期内完成大量计算;可以满足多目标模拟对高速运算的要求,所以在实现实时性上并不困难。

[1]. PCI datasheet https://www.dzsc.com/datasheet/PCI_1201469.html.

[2]. AD9857 datasheet https://www.dzsc.com/datasheet/AD9857_251854.html.

[3]. Memory datasheet https://www.dzsc.com/datasheet/Memory_1082507.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。