FPGA开发中常用到单脉冲发生器。一些文章介绍过产生单脉冲的电路,产生的单脉冲脉宽和相位都不能与时钟同步,只能用在要求不严格的场合。笔者目前从事的课题中需要一个与时钟周期等宽,相位与时钟周期相同的键控单脉冲发生器。键控单脉冲发生器需要按键产生单脉冲,但大多数带有FPGA芯片的开发板提供的是高频时钟脉冲,按键时会存在抖动问题。为此笔者专门设计了按键消抖电路消除抖动,为产生单脉冲提供稳定的按键信号。

1 按键消抖电路原理

为了使按键消抖电路模块简洁,移植性好,在此用计数器的方式实现按键消抖的功能。

计数器模值n根据抖动信号的脉冲宽度和采样脉冲信号CLK的周期大小决定。计数模值n=延时/脉冲信号采样周期。一般按键抖动时间为5~10 ms,甚至更长。笔者用的开发板提供的系统时钟为24 MHz,按公式计算,当计数器模值取20位,计数到219即h8 0000时,大约延时22 ms。计数期间认为是按键的抖动信号,不做采样;计数器停止计数,认为采样信号为稳定按键信号。这样就可以把按键时间小于22 ms的抖动信号滤掉。

引入一个采样脉冲信号CLK,并输入按键信号KEY。KEY输入低电平,计数器开始做加法计数,当计数到h8 0000即计数器中位Q19为1,计数器停止计数,输出Q19,作为按键的稳定输出,计数期间Q19输出为0;KEY输入高电平,计数器清零,Q19输出为0。所以该电路需按键22 ms才会得到有效信号。

2 键控单脉冲发生器电路原理

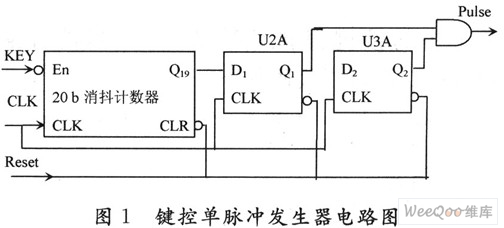

键控单脉冲发生器利用上述电路解决按键消抖问题,得到稳定的信号。用两个D触发器和一个与门产生单脉冲,如图1所示。

D触发器U2A收到稳定信号D1=1后被触发。触发器U2A中的Q1端得到与CLK同步的正向脉冲。输出Q1到D触发器U3A,得到比Q1延迟一个时钟周期的的正向脉冲,将Q2端输出取反得到一个负向脉冲。Q1与Qn2的输出作为一个与门的输入,会输出一个脉宽是原时钟周期2倍的单脉冲。

为了使得出的单脉冲脉宽与时钟周期相等,相位与时钟周期相同,对图1中电路设计做了改进,如图2所示。

图2中时钟送入D触发器前加了非门,使Q1端产生与nCLK(CLK的反向脉冲信号)同步的正向脉冲,与门输出单脉冲与CLK差半个时钟周期,作为D触发器U4A的输入D4,在CLK上升沿U4A被触发,使单脉冲脉宽与时钟周期相同,实现了等脉宽。并延迟了半个时钟周期使输出脉冲与时钟周期对应,实现了相位调整。整个单脉冲发生器的时序图如图3所示(图3中的t1,t2是任意键按下与键抬起时刻)。

3 基于FPGA下的按键消抖计数器和单脉冲发生器的Verilog HDL语言描述

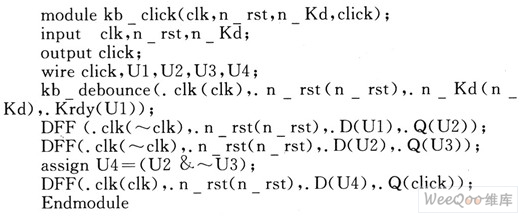

图1中的按键消抖计数器电路,其进行描述的Verilog HDL语言代码如下:

代码中的复位n_rst和按键n_Kd都是低电平有效。键控单脉冲发生器的Verilog HDL语言代码如下:

代码中还用到了D触发器DFF,实现这个模块的代码比较简单,此处从略。

4 结 语

该文中的设计,实现了键控单脉冲发生器,产生脉宽等于时钟脉冲,输出脉冲与时钟周期对应的单脉冲,并解决了按键消抖问题,可以应用到各种需要产生单脉冲的FPGA电路设计中。按键消抖电路可独立地应用于其他FPGA电路设计中。本文中设计的20 b计数器是根据笔者课题需要而定。其他设计中可以根据按键抖动时间可利用公式计算出计数器模值设计计数器。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。