0 引言

图像是自然生物或人造物理的观测系统对世界的记录,是以物理为载体,以介质来记录信息的一种形式。图像信息是人类认识世界的重要知识来源。据学者统计,人类所得的信息有80%以上是来自眼睛摄取的图像。而事实上,这种静态的图像已无法满足人们对视频信息的要求。随着人们对视频数据的要求越来越高,高清晰、实时性视频数据量越来越大,视频的实时处理难度也在逐渐增大。本文给出了一款基于DSP+FPGA的嵌入式实时视频采集系统的设计方法,该系统可以广泛应用于关系公共安全的场所,如银行、机场、车站、商场等。

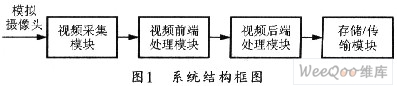

1 实时视频采集系统结构

常见的视频采集系统主要有两种:一种是基于单处理器(单片机、ARM等)的视频采集卡,特点是结构简单,易于实现,缺点是无法实时地对视频数据完成处理,需要使用外部处理器来完成特定的视频处理算法,因而成本高,升级维护难度大;另一种是基于主从处理器(ARM+DSP,FPGA+DSP等)的嵌入式视频采集卡,特点是系统高度集成,易于维护升级,可以满足视频采集的需求,同时可以完成特定的视频算法,成本较低。因此,本文给出了一种基于DSP+FPGA的嵌入式视频采集系统设计方案。其系统结构框图如图1所示。

2 系统硬件设计

本系统的设计思路是通过模拟的视频摄像头来获取视频信号,然后采用模数转换芯片SAA71 11A将模拟的PAL制式视频信号转换为YUV4:2:2的数字视频信号。设计使用FPGA芯片EP1C6Q240C8作为协处理器,来完成视频信号的缓存和视频帧的合成,通过双RAM的乒乓结构来实现视频帧的完整性,并在完成视频数据的预处理后,将视频数据传入到DSP中,完成特定的视频处理算法(如压缩等),对处理完的视频数据进行传输和存储。同时,主处理器DSP还负责对视频采集芯片进行初始化配置。其系统硬件结构如图2所示。

2.1 视频采集模块

设计一个视频采集系统的重要环节,通常是将外部的光信号转换成电信号,然后通过专用的视频转换芯片,来将模拟的视频信号转换为数字视频信号。本设计采用的是模拟CMOS摄像头和Philips公司的高性能视频模数转换集成电路芯片SAA71 11A。

SAA7111A是Philips公司的一款高性能视频输入处理芯片。它共有四路模拟视频信号输入端,可以输入4路CVBS或2路S视频(Y/C)信号,也可以编程选择四路视频输入中的一路或者两路组成不同的工作模式;可实现行同步、场同步信号的自动监测、分离,或场频50 Hz或60 Hz自动检测,并可在PAL制和INTSC制之间自动切换,同时能对不同输入制式的亮度信号、色差信号进行处理,实现亮度、色度和饱和度的片内实时控制;SAA7111A中的I2C总线接口可以对片内寄存器进行设置。它有32个控制寄存器,其中的22个可编程;该器件的输出为16位V.PO总线,输出格式有12位YUV4:1:1、16位YUV4:2:2、8位CCIR-656、16位565RGB和24位的888RGB;输出信号可提供采样时钟、行同步、场同步等多种同步信号。

SAA7111A可将PAL制式的模拟视信号频转化为YUV4:2:2的16位数字视频数据,大小为625×720×16 bit,其中25行用作场回扫,因此,每帧的有效数据有576×720×16 bit。

2.2 视频前端处理模块

数字化后的视频数据量一般都十分巨大。为了保证视频数据的完整性和实时性,系统专门设计了视频的前端处理模块。其主要功能是完成视频数据的缓存,视频帧的合成,乒乓操作以及与DSP的通信。由于FPGA内部能反复编程,可以使系统简化,减小板卡面积,易于维护,升级方便,因此,本文采用了ALTERA的EP1C6Q240C8来完成视频前端处理功能。

由于该视频转换芯片没有提供地址信号,所以需要在FPGA内部设计一个地址产生器,以使数据可以对应的存储起来。SAA7111A提供有4个重要信号:LLC(参考时钟信号)、HREF(水平参考信号)、VREF(垂直参考信号)、RTSO(奇偶场信号)。

由于PAL制式具有隔行扫描特性,因此,采集的视频数据可被分为奇偶场。因为视频图像处理是针对完整的视频帧,所以需要将奇偶场的视频数据进行合成。其实现方法是奇偶两部分合成一帧数据,即:偶场地址=基地址O+偏移地址;奇场地址=基地址E+偏移地址。帧合成操作示意图如图3所示。

为了保证视频采集系统的实时性,该系统使用双RAM的乒乓机构。乒乓操作在FPGA时序设计中的使用十分广泛,是一种典型的以面积换速度的设计思想。这种结构是将输入数据流通过输入数据选择单元等时地将数据流分配到两个数据缓冲区。在第1个缓冲周期,将输入的数据流缓存到数据缓冲模块1上;在第2个缓冲周期,则通过输入数据选择单元的切换来将输入的数据流缓存到数据缓冲模块2,同时将数据缓冲模块1缓存的第1个周期的数据通过输出数据选择单元的选择后,送到运算处理单元进行处理;此后在第3个缓冲周期,再次切换数据的输入与输出缓冲模块。如此循环,周而复始。其具体状态机如图4所示。

系统中的通信模块主要是在DSP处理完数据后给FPGA发送一个信号,以通知DSP处于空闲状态,当FPGA内部模块收到后,再将数据传输到DSP上。

2.3 视频后端处理模块

本系统采用的是,TI公司的高性能、低功耗定点DSP芯片TMS320VC5509A,它内部的主时钟工作频率可达200 MHz,处理速度400MIPS;该DSP的片上RAM较大,包括32 K×16位DARAM和96 K×16位SARAM,共128 K×16位的片上存储空间;其片上外设丰富,包括实时时钟RTC、10位ADC、MCBSP接口、USB高速接口(速率为12Mb/s),还有MMC/SD(多媒体卡)接口、I2H接口等;该DSP处理器为低电压供电,采用1.6 V的内核电压。3.3 V的I/O电压,功耗低达0.2 mW/MIPS。

DSP作为视频采集系统的主处理器,主要完成各类接口和外设的配置以及视频的实时处理。包括时钟发生器(PLL)、I2C总线接口、EMIF模块、USB接口等。

各类接口只有协调工作,才可保证系统的正常运行。其中时钟发生器负责将外部24 MHz的晶振时钟倍频为200 MHz的系统工作时钟:I2C总线负责对视频采集芯片SAA711 1A进行初始化配置:USB接口负责与上位机通信,以实现数据的传输。

考虑到视频数据的庞大和DSP片上ROM的局限性,本系统在DSP外部扩展了一块4 M×16 bit的SDRAM和一块256 K×16 bit的FLASH。其中SDRAM映射在DSP的CE2、CE3空间,FLASH映射在CE1空间。由于外设接口配置一般都较为复杂,因此使用了TI公司的片上支持库函数(CSL),以简化用户接口的配置。

视频数据中一般都会存在很多冗余信息(时间冗余度、空间冗余度等),因此具有压缩的必要性。视频编码的主要目的就是在保证重构质量的前提下,以尽量少的比特数来表征视频信息,尽量去除视频图像数据本身具有的多种冗余特性,如空间冗余、时间冗余、心理视觉冗余和熵编码冗余等。常见的压缩标准有JPEG、MPEG-1、MPEG-2、H.261以及H.263等。这些算法一般都较为复杂,处理的数据量也十分巨大。而采用哈佛总线和流水线操作等内部结构DSP在视频处理算法的实现上具有巨大优势。视频算法的编程和调试可在CCS(code composer studio)2.0环境下完成,可使用C语言实现,这样有利于跨平台的移植、优化和升级。

3 结束语

本文所设计的基于DSP+FPGA的实时视频采集系统,采用双RAM的乒乓结构来实现对视频的实时采集,利用DSP主处理器来实现JPEG压缩算法,同时使用在线编程技术并利用JTAG对系统进行在线调试。因此,该系统具有体积小、成本低、功耗低、速度快、适应性强、便于维护等特点,因此,在图像的实时处理方面具有良好的应用前景。

[1]. EP1C6Q240C8 datasheet https://www.dzsc.com/datasheet/EP1C6Q240C8_1135222.html.

[2]. SAA7111A datasheet https://www.dzsc.com/datasheet/SAA7111A_595760.html.

[3]. TMS320VC5509A datasheet https://www.dzsc.com/datasheet/TMS320VC5509A_688864.html.

[4]. ROM datasheet https://www.dzsc.com/datasheet/ROM_1188413.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。