Cadence 宣布推出其版Cadence? Allegro? 与 OrCAD?印刷电路(PCB) 软件,它拥有的全新功能与特性能够提高PCB工程师的绩效与效率。Allegro与OrCAD PCB Design 16.3版本为PCB工程师带来了极大的新优势,包括改进终端产品小型化设计能力并减少原型机设计的反复次数,使得设计周期更具可预测性。

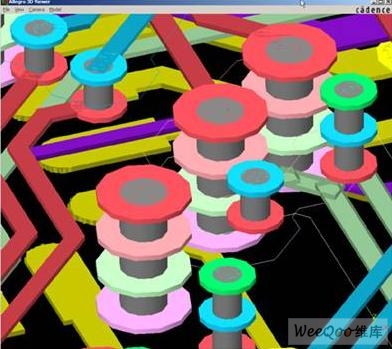

本版本包括一些新增功能和互连密度的改进,如刚柔布线,扩展的高密度互连(HDI)规则、PCB的三维(3D)显示与RF电路的非对称避让。拓展的微孔叠层规则允许用户创建极为复杂的HDI设计,而与柔性板轮廓吻合的多线式曲形总线布线会加快刚柔设计。此外,集成的3D PCB浏览器让设计师可以看到元件与HDI微导孔内部,从而为机械设计团队消除了不必要的迭代。Allegro PCB RF选件还通过使用一个或多个RF元件的非对称避让帮助工程师加快创建RF电路的速度。

新版Allegro与OrCAD使用多阶段预发布的方式确保内容与质量能够符合客户的需要。来自北美、欧洲、亚洲和日本的20多家客户参与了多阶段测试计划。参与测试计划的客户与Cadence的合作伙伴包括NVIDIA、Emerson、Kaleidescape、Freedom CAD、NordCAD、FlowCAD、Graser与Tektronix。

16.3版本中还包含对OrCAD系列产品应用效率与可用性的一系列大幅改良。例如OrCAD Capture CIS如今提供了自动布线功能以迅速增加连线,还有全新的三维封装显示功能。OrCAD PCB Editor提供了三维查看与“翻板”设计/编辑以及单面PCB设计的跳线支持。OrCAD Signal Explorer有一个经改良的用户界面,有拖拽和复制粘贴功能,有前后关联的右击功能并支持本地IBIS模型。

可用性改进是新版Allegro PCB信号与电源完整性软件的又一个重点,它提供了一个全新的用户界面,并为预布线分析环境增加了叠层感知功能。通过对本地IBIS与SPICE模型包括Cadence Virtuoso? Spectre? 电路仿真模型的支持, I/O缓冲器建模标准也包含在其中。另外一个改进设计周期管理的地方是能够用大量吉比特级信号快速扫描PCB,并且迅速确定应该在哪里进行详细分析,信号会根据其信噪比进行排列。

该版本解决的另外一些重要问题是与部件数据管理有关。集成的ECAD、MCAD部件创建,生成与发布可以降低不必要的原型机出样次数。这个新部件导入功能可以扩展预发布与临时部件的管理与通知,缩短设计周期。此外,工程师可以通过使用批准的与推荐的部件替换原来的部件来实现自动部件更新,也可以通过废弃部件跟踪以确保产品的质量。

Allegro与OrCAD PCB Design 16.3版将于2009年12月初开始向客户提供。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。