0引言

边缘检测技术是图像处理的一项基本技术,在工业、航天、医学、军事等领域中有着广泛的应用。边缘检测算法的实现涉及复杂的计算步骤,故对处理速度有较高要求。采用FPGA器件实现系统设计是一种纯硬件的解决方案,该方案可以使系统具备较高的实时性,能比较好地解决软件编程方式所导致的处理速度问题。

1 Sobel算法

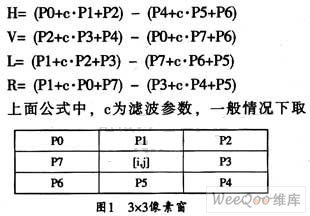

在众多的图像边缘检测算法中,Soble算法具有计算简便、检测效果好等优点,是一种被广泛应用的算法。Sobel算法依据图像边缘的灰度值会产生突变的原理,来对像素的灰度值进行处理。在图1所示的3×3像素窗中,中间像素[i,j]为待检测像素,Sobel算法分别对此像素窗进行水平(H)、垂直(V)、左对角(L)、右对角(R)四个方向的灰度值滤波运算,公式如下:

c=2。这里的H,V,L,R是为了计算梯度的大小和方向。梯度大小可由下式得到普遍估计:

若此幅值大于给定的某阈值,则可判定像素点[i,j]为边缘像素,否则为一般像素。梯度方向与四个滤波值中的方向一致。

2 系统设计

一个完整的图像边缘检测系统主要包括以下三个功能模块:像素窗生成模块、边缘检测模块以及输出处理模块,图2所示是边缘检测系统示意图。其中像素窗生成模块主要负责生成供边缘检测模块计算的3×3像素窗;边缘检测模块采用Soble算法对此像素窗进行处理,以判断中心像素是否为边缘像素;输出处理模块负责后续处理任务(如生成完整的边缘图像)。

2.1 系统设计思路

本文主要讨论边缘检测模块的设计。这里使用行为域建模的方式对系统进行算法描述。该方法可以使系统行为与结构相分离,设计者只需对系统的功能进行算法描述而不必关心系统具体的硬件构成方式。这种设计方法在设计过程中借鉴了软件设计的灵活性优点,而设计结果则是具有高运算速度的硬件电路。

这种设计思路不必依次设计加法器、寄存器、比较器等功能单元。由于Sobel算法中的边缘检测主要包含两个步骤:一是对像素窗进行四个方向滤波;二是对滤波值进行决断。因此,可采用状态机方式来描述系统功能。但这里需要三个状态:空闲态(IDLE)、滤波态(FILTER)和决断态(JUDGE),图3所示是其系统状态图。

图3中的IDLE为边缘检测模块默认的初始状态,此状态下不进行任何处理动作。如果模块接收到有效的检测启动信号,则转入FILTER状态。在此状态下,模块对输入的像素窗进行四个方向的滤波处理。下一时钟周期到来后则转入JUDGE状态,此状态下,模块进行边缘判断,并输出相应结果。经过这样一个过程后,即可完成一个像素窗的处理,之后,如果检测启动信号继续有效,则转入FILTER状态并处理下一个像素窗,否则转入IDLE状态待命。

2.2系统实体设计

依据上述设计思路,可以设计出如图4所示的边缘检测模块的顶层实体。其中START为来自外界的检测启动信号输入,用于启动边缘检测;CLK为时钟信号输入,是状态机的驱动时钟;数据输入端口P0~P7分别接收像素窗中相应像素的8位灰度值;POUT为检测结果灰度输出,输出0表示非边缘像素,输出255表示边缘像素;DIR为方向输出;FINISH为检测结束信号输出,用于配合其它模块协同工作。

2.3系统行为描述

由于设计采用行为建模,因此,系统描述不涉及任何硬件器件以及连接相关,只需在结构体中设置两个进程来描述状态机,并定义相关变量和函数就可以完成对此系统的描述。

为描述系统行为,首先应定义如下信号:

其中,信号ST表示状态机状态;HF、VF、LF、RF分别用于存储四个方向滤波值;MAG存储依据四个滤波值得出的梯度幅度值。

进程CHANGESTATE可完整描述状态图中各状态间的转移关系。此进程由敏感信号CLK进行驱动,并在时钟上升沿到来时,可通过判断当前状态以及相关转移条件来确定状态机的次状态。其完整的代码如下:

进程STATEBEHAVIOR主要负责处理状态机特定状态下的行为输出。此进程由状态信号ST作为敏感信号进行驱动。在空闲态(ST=IDEL)时,系统初始化相应输出;而在滤波态(ST=FILTER)时,系统则调用四个函数H_FILTER ()、V_FILTER()、L_FILTER()和R_FILTER()并依照Soble算法进行滤波计算;决断态(ST=JUDGE)时,则调用函数MAGNITUDE ()和PHASE ()来计算梯度的大小和方向,并通过决断后输出处理结果,同时使检测结束信号有效(FINISH='1')。其完整代码如下:

以上全部代码中使用的数据类型和函数均已在PIXEL_PROCESSING.vhd文件中定义,因此,设计时只需在本VHDL文件中使用use子句将其作为设计库中的包进行引用即可,其代码如下:

use work.PIXEL_PROCESSING.all;

通过采用以上VHDL语言行为域进行描述,即可完成基于Soble算法的图像边沿检测模块的设计。

3仿真分析

采用两个数据窗可对系统进行功能仿真。从图5所示的仿真时序中可以看出,两个时钟周期可完成一个数据窗的处理,个时钟周期生成滤波值VF、VH、VL和VR,第二个时钟周期生成幅值MAG并产生判决结果POUT。当用40 MHz时钟时,若能以此时钟二分频的速度连续产生数据窗,则处理一个像素只需50 ns,也就是说,处理一个800×600的图像只需24 ms。此时,系统处理速度的瓶颈已不在边缘检测模块,而由其它模块,如像素窗的生成速度所决定。

除此之外,第二个时钟周期所产生的有效检测结束信号(FINISH)既可以作为前端模块的数据窗发送信号,也可以作为后端模块的检测结果接收信号。该信号对模块间的协同工作具有重要的意义。

4结束语

采用FPGA器件实现Soble算法的图像边缘检测具有设计过程简单,处理速度快等优点。该方法将前端的像素窗生成模块、后端的图像处理模块以及其他功能模块集成至同一FPGA器件中,从而大大提高了系统的集成度。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。