内容可寻址存储器CAM(Content-Addressable Memory)是以内容进行寻址的存储器,是一种特殊的存储阵列RAM,它的主要工作机制就是将一个输入数据项与存储在CAM中的所有数据项自动同时进行比较,判别该输入数据项与CAM中存储的数据项是否相匹配,并输出该数据项对应的匹配信息,美国Motorola公司的CAM芯片MCM69C232在市场上是性价比较高的产品,因而被广泛地应用于网络通信,模式识别等领域,其用于数据检索的优势是软件无法比拟的,可以极大的提高系统性能。

1 MCM69C32芯片介绍

内容可寻址存储器(CAM)从本质上讲是一种基于RAM技术的特殊存储器,数据项存储在CAM内部的阵列单元中,每个数据项中的位数称为"字宽",阵列内所有数据项的条数称为"深度",CAM的容量通过字宽和深度来表征,MCM69C232设计可存储4096条宽度为64位的数据项。

MCM69C232有两组数据端口:控制端口(control port)和匹配端口(match port)。控制端口用于处理器(CPU)对CAM表的操作,包括插入、删除数据表项、模式设置和模拟匹配,以及读取芯片内部状态寄存器的信息等,数据项的检索通过匹配端口完成。

尽管基于RAM技术,但CAM的存储机制却与RAM大相径庭,图1为MCM69C232的结构框图,图中MCM69C232没有用于确定内容存储单元的地址总线,其地址线A0-A2用于对片内控制寄存器的寻址。处理器通过操作MCM69C232的控制端口(数据线DQ0-DQ15)可以读/写CAM表中的数据项,数据项的存储地址由芯片内部逻辑控制。MCM69C232有两种工作模式:ATM模式和基本模式。ATM模式主要用于ATM交换机对ATM信元进行虚拟通路标识号/虚拟通道标识号(VPI/VCI)的转换处理,基本模式主要用于以太网上的IP/MAC地址匹配等数据检索。

|

MCM69C232芯片的主要特性如下:

160ns的匹配时间;

没有屏蔽寄存器;

通过芯片级联扩展深度;

时钟频率为50MHz;

匹配字宽和输出结果位宽可自定义;

在ATM模式下可进行VPC(Virtual Path Circuits)和VCC(Virtual Connection Circuits)的同时匹配;

端口主要分为控制和匹配端口;

200ns的插入时间(在12个端口数据项队列未满的情况下);

12ms的初始化时间(在设置了快速写入模式后);

具有符合IEEE标准1149.1的测试端口(JTAG)。

2 MCM69C232芯片的使用

在基本操作模式下,MCM69C232的读取输入数据并与CAM表中的所有表项相比较,无论匹配项找到与否,当比较完成后,MC(Match Complete)引脚均有效,如果找到了匹配项,则MS(Match Successful)引脚有效,同时在MQ总线上输出与匹配数据项相关的数据,如果没有找到,则MQ总线保持高阻态,以便级联CAM芯片来扩展存储深度。

MCM69C232上电后,默认工作模式为基本模式,在进入数据检索操作之前,芯片必须先完成几个启动操作过程:首先,要设置全局屏蔽寄存器,定义匹配字宽和输出结果位宽;其次,要选择数据表项的写入模式,即快速写入模式还是动态写入模式;再次,要把用户需要的数据项(共64位,包括匹配字节和与其对应的输出结果字节)逐次装入CAM表中。

CAM表数据项写入模式的选择,往往是在写入速度和启动匹配操作花费的时间中取个平衡,快速写入模式,常用于将大量的数据项初始写入CAM表中,而动态写入模式,则常用于启动匹配后往CAM表中插入少量的数据项。用户通过操作控制口4个I/O寄存器来插入或删除CAM表项,当有异常状态出现时,可以从标志寄存器和错误代码寄存器反应出来,MCM69C232内部的寄存器如图2所示。

|

MCM69C232芯片的主要特性如下:

160ns的匹配时间;

没有屏蔽寄存器;

通过芯片级联扩展深度;

时钟频率为50MHz;

匹配字宽和输出结果位宽可自定义;

在ATM模式下可进行VPC(Virtual Path Circuits)和VCC(Virtual Connection Circuits)的同时匹配;

端口主要分为控制和匹配端口;

200ns的插入时间(在12个端口数据项队列未满的情况下);

12ms的初始化时间(在设置了快速写入模式后);

具有符合IEEE标准1149.1的测试端口(JTAG)。

2 MCM69C232芯片的使用

在基本操作模式下,MCM69C232的读取输入数据并与CAM表中的所有表项相比较,无论匹配项找到与否,当比较完成后,MC(Match Complete)引脚均有效,如果找到了匹配项,则MS(Match Successful)引脚有效,同时在MQ总线上输出与匹配数据项相关的数据,如果没有找到,则MQ总线保持高阻态,以便级联CAM芯片来扩展存储深度。

MCM69C232上电后,默认工作模式为基本模式,在进入数据检索操作之前,芯片必须先完成几个启动操作过程:首先,要设置全局屏蔽寄存器,定义匹配字宽和输出结果位宽;其次,要选择数据表项的写入模式,即快速写入模式还是动态写入模式;再次,要把用户需要的数据项(共64位,包括匹配字节和与其对应的输出结果字节)逐次装入CAM表中。

CAM表数据项写入模式的选择,往往是在写入速度和启动匹配操作花费的时间中取个平衡,快速写入模式,常用于将大量的数据项初始写入CAM表中,而动态写入模式,则常用于启动匹配后往CAM表中插入少量的数据项。用户通过操作控制口4个I/O寄存器来插入或删除CAM表项,当有异常状态出现时,可以从标志寄存器和错误代码寄存器反应出来,MCM69C232内部的寄存器如图2所示。

CAM表的匹配位取决于全局屏蔽寄存器的定义,屏蔽寄存器为0的位要求数据项的对应位作匹配操作;为1,则对应位无需匹配,典型的应用中用户总是把数据项的高位序位定义为"待匹配字节",低位序位定义为"结果输出字节"。64位中的任何位都可以定义为"匹配操作",但实际上输出到匹配口MQ0-MQ31总线上的总是32位数据,并非可任意编程输出的。如果设置的输出结果字节超过32位,则是无意义的。

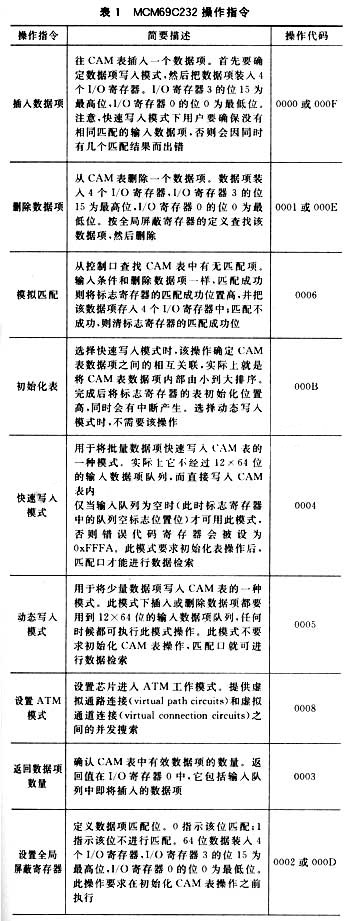

通常情况下,MCM69C232通过写控制口数据和指令来准备匹配操作,一般步骤是把数据项装入4个I/O寄存器,然后往操作代码寄存器写入操作代码,即可完成一种指令的操作,指令完成后CAM表的内容可能会被修改,标志寄存器的相应位会被置位,错误代码寄存器会返回错误码,当使能时,还会触发中断。

芯片的操作指令如表1所列。

|

复位。复位同步于主时钟的上升沿,一个时钟周期的复位就能清空CAM表和输入数据项队列,置标志寄存器为1C,错误代码寄存器为FFFF,几乎满寄存器FFF,并清除中断屏蔽。

控制口时序,访问控制口如同处理器访问RAM一样,时序较为简单。

匹配口时序,访问匹配口分两种情况:一种是匹配字节小于等于32位,只用LH/SM信号装载匹配数据,LL信号无用,另一种是匹配字节大于32位,先用LL信号装载匹配数据低位部分,再由LH/SM信号装载高位部分,匹配结果由MC信号和MS信号指示,使能G信号读取匹配结果数据,匹配口时序参见参考文献[1]。

两口同时匹配,控制口模拟匹配和匹配口匹配同时进行时,匹配口优先权较高,另外控制口模拟匹配操作之前要求输入队列为空,以便接收结果。

深度扩展。芯片简单级联即可扩展深度,具体的扩展连接方法请参见参考文献[1]。

3 MCM69C232芯片的应用

3.1 MCM69C232在交换机中的应用

在以太网上,交换机维护一张用于二层交换的地址表(通常称为"CAM表"),该表维护MAC地址与出接口的对应关系,这样每当接收到一个以太网数据帧,交换机就会进行判断,如果该数据帧不是发送给自己的,则根据数据帧的目的MAC地址查询CAM表,如果能命中(所谓命中,就是在CAM表中找到与该MAC地址对应的转发项),则根据查询的结果(通常是一个出接口列表)进行转发;如果不能命中,则向所有端口广播该数据帧。

交换机的这张CAM表可以通过多种方式获得,比如静态匹配、动态学习。针对多播,还可以通过各种多播协议(如IGMP窥探、GMRP协议等方式)获得(多播转发表不能通过学习获得,而且多播转发项跟普通转发项不同,与其对应的出口可能不只一个,而是一个出口集合);但对于单播,重要的一种建立方式是动态学习。

当交换机接收到一个数据帧时,提取出该数据帧的目的MAC地址,并以此为根据进行CAM表查询,如果能查找到结果,则根据结果进行数据帧的转发,如果不能命中,则对除接收端口外的所有端口进行复制。在进行数据转发的同时,交换机还进行一个学习的过程,它把数据帧的源MAC地址提取出来,查询CAM表,看CAM表中是否有针对该MAC地址的转发项,如果没有,则把该MAC地址和接收到该MAC地址的端口绑定起来,插入CAM表项,这样当接收到一个发送到该MAC地址的数据帧时,就不需要向所有端口广播,而仅向这个端口发送即可,需要注意的是,数据帧的转发是依据目的MAC地址查询MAC表,而CAM表的学习则是以源MAC地址为依据的。

之所以在交换机中使用CAM,是因为交换机对性能要求特别高, 交换机中的嵌入式实时控制系统的性能主要取决于两方面:硬件平台的运算性能和算法优越性,其中,硬件平台的运算性能为关键,这一点在交换机中表现的尤为突出,按照设计要求,以太网帧的MAC地址的检索时间一般都是μs级,因此首先要保证数据检索任务的响应速度;除了十分繁重的数据检索任务外,交换机还必须完成SNMP(Simple Network Management Protocol)协议处理、命令行处理等任务,所以还必须解决数据检索对系统资源的占用问题,利用软件实现对以太网帧的MAC地址检索并不复杂,但由于检索次数频繁,大量的系统资源被占用,致使系统的响应速度大大降低,满足不了大流量数据通信的要求,因此纯软件算法解决不了数据检索部分占用大量资源的问题,为提高系统的响应速度,必须将数据检索的任务分离出来由硬件实现,而协议处理部分仍由CPU完成,数据检索模块和协议处理模块并行工作,利用硬件实现数据检索还可以提高检索速度,降低系统资源的占用率。在这里CAM的优势就体现出来了。

|

3.2 检索操作

当进行MAC地址检索时,CPU首先以MAC地址为关键字通过MAC-CAM表的检索得到对应的索引值,然后再根据索引值找到RAM表中该MAC地址对应的相关信息的存储位置,并也此地址获得相关配置信息,在RAM中的相关配置中可以存放诸如MAC地址、用户端口、有效标志域等其他信息。CAM表示RAM的映射关系如图3所示。

按协议规定MAC地址占48位,表示为6字节的数组,故对于MAC地址的匹配操作,屏蔽字设为0x0000_0000_0000_FFFF,即48位匹配,屏蔽字的设定必须在CAM初始化时完成,在执行匹配操作前,CAM须进行初始化,MCM69C232上电后,默认工作模式为基本模式,因此不必再设置工作模式,前面已提到过,CAM中MAC表的形成是通过自学习得到的,因此无需向CAM表中写入数据项。

匹配操作通过对匹配口读/写来完成,匹配口数据线MQ只有32位,由于MAC地址占48位,因此需要两次写操作才能完整地将一个MAC地址表达出来,当进行MAC地址检索时,CPU先向匹配口写入MAC地址的低32位数据,其中高16位有效,低16位可以为任意值;紧接着CPU向匹配口写入高32位数据,随后CPU读匹配口,即可得到匹配结果。

[1]. MCM69C232 datasheet https://www.dzsc.com/datasheet/MCM69C232_864945.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。