摘要:在分析高速数字电路设计中存在的几个主要问题的基础上,探讨了高速信号完整性所涉及到的基本理论研究了在PCB仿真设计实际应用中通常采用的两种模型方法,即IBIS模型和SPICE模型,分析了仿真模型和建模方法。结合一个具体高速电路设计——小型封装可热插拔式光纤收发模块(SFP)的反射仿真实例,讨论了仿真模型的建立并对仿真结果进行了分析,研究结果表明在高速电路设计中采用基于信号完整性的仿真设计是可行的,也是必要的。

关键词:高速数字电路;信号完整性;仿真模型;PCB

引言

目前,国内外有关信号完整性(signal integrity,SI)工程和研究还是一门尚未成熟的学科,其分析方法和实践都没有很好地完善,还处于不断的探索阶段。在基于信号完整性计算机分析的PCB设计方法中,为的部分就是PCB板级信号完整性模型的建立,这是与传统的设计方法的主要区别之处。SI模型的准确性将决定设计的正确性,而SI模型的可建立性则决定了这种设计方法的可行性。

高速数字电路设计方面的问题突出体现为以下类型:(1)工作频率的提高和信号上升/下降时间的缩短,会使设计系统的时序裕量缩小甚至出现时序方面的问题;(2)传输线效应导致的信号震荡、过冲和下冲都会对设计系统的故障容限、噪声容限以及单调性造成很大的威胁;(3)信号沿时间下降到1ns以后,信号之间的串扰就成为很重要的一个问题;(4)当信号沿的时间接近0.5ns时电源系统的稳定性问题和电磁干扰(EMI)问题也变得十分突出。

在高速系统中,能否处理好系统的信号互连,解决信号完整性的问题,是系统设计成功的关键。同时,信号完整性也是解决电源完整性、电磁兼容与电磁干扰(EMC/EMI)问题的基础和前提。

高频效应与传输线理论

高频效应

集肤效应 在高频情况下,电磁波进入良导体中会急剧衰减,甚至在还不足良导体中一个波长的距离上,电磁波已受到显著衰减,所以高频电磁场只能存在于良导体表面的一个薄层内,这种现象被称为集肤效应。电磁波场强振幅衰减到表面的1/e的深度则为趋肤深度

![]()

式(1)说明:电导率越大即导电性越好,工作频率越高,趋肤深度越小,其导致高频时的电阻远大于低频或直流时的电阻。邻近效应 在若干个载流导体间的相互电磁干扰时,各载流导体截面的电流分布与孤立载流导体截面电流分布是不同的。当存在通有相反方向电流的两邻近导体时,在相互靠近的两侧面近点电流密度;当两载流导体电流方向相同时,则两外侧面的电流密度。一般情况下,邻近效应使得等效电阻加大,电感减小。

传输线理论

广义传输线是引导电磁波沿一定方向传输的导体、介质或由它们组成的导行系统。一般所讨论的传输线是指微波传输线,其理论是长线理论。而当传输线的几何尺寸与电磁波的波长可以相比拟时,必须考虑传输线的分布参数(或称寄生参数)。在高速数字或射频电路设计和高速电路的仿真设计中,许多电磁现象必须应用传输线理论进行解释,传输线理论是研究高速数字(或射频)电路的基础。

基本传输线理论 当传输信号速率或频率达到一定时,传输信号的通道上的分布参数必须考虑。以平行双导线为例,其上的集肤效应带来单位长度射频阻抗增大。当其达到射频段,平行双线周围的磁场很强,必须考虑其寄生电感,且平行双线间的电场要用电容来等效。同时,导线间在频率很高时还要考虑导线间的漏电现象。所以一条单位长度传输线的等效电路可由R,L,G,C4个元件组成,如图1所示。

图1 单位长度传输线之等效电路

由克希霍夫定律可得传输线方程表示式为

因此,传输线方程的通解可写成

![]()

式中:V+ ,V- ,I+ ,I-分别是电压波和电流波的振幅常数,而+、-分别表示入射波(+Z)及反射波(-Z)的传输方向。传播常数C定义为

![]()

式中:A为衰减常数;B为相位常数。传输线上一点的电压和电流分别是入射波与反射波的叠加。在Z轴上任一点的电压及电流表达式为

![]()

![]()

上式说明在一传输线上传输的电压波和电流波是时间及传输距离的函数。

集成传输线理论

集成传输线包括微带线、带状线、耦合线和各种共面波导。微带线目前是混和微波集成电路和单片微波集成电路中使用多的一种平面型传输线。它可用于光刻程序制作,且容易与其他无源微波电路和有源微波器件集成,实现微波部件和系统的集成化。微带线的信号线在外层,地层在信号线的另一边,易于测试。

带状线又称三板线,由两块矩形截面导体带构成,接地板之间填充均匀介质或空气。带状线的信号线夹在两个电源层之间,理论上它能地传输信号,因为它两边都有电源层的屏蔽。但它将信号线隐藏在内部不利于测试。

信号完整性理论

信号完整性(SI)主要研究的是信号沿导线传输后的质量和时序问题。通常,需要解决的信号完整性问题包括:(1)反射,由于阻抗不匹配引起;(2)串扰,由相邻信号耦合产生;(3)过冲和下冲;(4)振铃,表现为信号反复振荡,可以通过适当的端接来抑制;(5)地平面反弹噪声与开关噪声,对于高速器件,大量数据总线信号快速翻转,通过地回路的电流变化导致非理想的地平面;(6)电源分配,对于高速电路来说,控制好电源/地平面的阻抗是系统设计的关键;(7)时序问题,对于高速设计,信号的传播延时、时钟偏移和抖动等因素足以导致系统无法正确判断数据;(8)EMI问题,包含电磁辐射和抗扰性两个方面的问题,解决PCB设计中的EMI问题是系统EMI控制中为重要的环节,成本也。

仿真模型与建模方法

SPICE仿真模型及建模方法

SPICE仿真模型 SPICE(simulation program with integrated circuit emphasis)是一种通用电路分析程序,能够分析和模拟一般条件下的各种电路特性。

SPICE程序能够代替面包板、示波器等整个电子实验室的功能。SPICE程序具有庞大的器件库,其中包括:(1)无源器件模型,如电阻,电容,电感,传输线等等;(2)半导体器件模型,如二极管,三极管,结型场效应管,MOS场效应管等;(3)各种电源,包括线性和非线性的受控源,如独立电压源、电流源,受控电压源、电流源等;(4)A/D,D/A转换接口电路以及数字电路器件库。

SPICE模型的建模方法 通常使用的器件有两种,一种是分立元器件,一种是芯片。根据器件的种类采取两种电路建模方法。

1)基本器件模型。例如:电阻、电容、电感、普通三极管等,这些是构成一个电路的基 本的单元。通常采用物理法来建模,即以描述器件的物理性能的方程为出发点来建立器件的模型。同样一个器件不同工作频率下的模型是不同的。

2)芯片子电路器件模型。芯片通常都是由一些基本的元件组成,把各个基本单元元件及其连接关系以网表的形式做成子电路,供其他的电路调用,就构成了一个芯片的子电路模型。通常采用黑箱(Blackbox)法来建模,即是把器件看作黑箱,着眼于端口的工作特性,用它构成模型。

IBIS仿真模型及模型结构

IBIS仿真模型 IBIS(input/outputbuffer information)输入/输出缓冲器信息规范,是一个元件的标准模型信息。IBIS模型是一种基于V/I曲线的对I/O缓冲器快速准确建摸的方法,是反映芯片驱动和接收电气特性的一种国际标准,它提供一种标准的文件格式来记录如驱动器输出阻抗、上升/下降时间及输出负载等参数,非常适合做振铃(ringing)和串扰(crosstalk)等高频效应的计算与仿真。

IBIS模型结构 IBIS模型是用于描述I/O缓冲信息特性的模型,一个输出输入端口的行为描述可以分解为一系列的简单的功能模块,由这些简单的功能模块就可以建立起完整的IBIS模型,即在一个缓冲单元中的基本元素,包括封装所带来的寄生参数(输入、输出或使能端)、硅片本身的寄生电容、电源或地的嵌压保护电路、门限和使能逻辑、上拉和下拉电路等。

PCB仿真实例及其结果分析

PCB板仿真相关参数的设置

印制电路板仿真有两种:线仿真和板级仿真。线仿真可以根据设计时对信号完整性与时序的要求,在布线前帮助设计者调整元器件布局、规划系统时钟网络以及确定关键线网的端接策略,在布线过程中跟踪设计,随时反馈布线效果。板级仿真通常在PCB设计基本完成之后进行,可以综合考虑如电气、EMC、热性能及机械性能等方面这些因素对SI的影响及这些因素之间的相互影响,从而进行真正的系统级分析与验证。在进行仿真时,首先要加载元器件的仿真模型,然后进行前仿真来确定布线过程中需要的参数设置和一些约束条件,接下来在实际布线过程中随时通过线仿真检查布线的效果,在布线基本完成之后进行板级仿真来检查系统工作的性能[6]。文中实例是对SFP(small form-factor pluggable optical transceiver)小型封装可热插拔式光纤收发模块进行的反射仿真分析。

仿真实例及结果分析

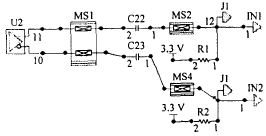

仿真模型的建立 在SFP光收发模块的原理图设计完成后,就要开始进行PCB板的设计。由于SFP光收发模块的工作频率设置为1.25Gbit/s,数据速率很高,而差分走线的长度很长,因此必须采用微带传输线进行阻抗匹配来减小在源端和终端的反射,从而确保信号的质量。根据原理图中MAX3748的芯片资料可知,其差分线的单端输出阻抗为50Ω,而根据SFP-MSA协议,主机板上的接口部分即RD+/-端口的差分阻抗为100Ω。根据差分线的理论,在没有耦合的情况下,两根平行的微带线传输线的差分阻抗等于单端阻抗的2倍,因此,必须采用特性阻抗为50Ω的传输线来进行匹配。提取MAX3748和接插件J1之间互连网络的拓扑如图2所示。由于J1是接插件,没有相应的IBIS模型数据可以调用,因此为了使得仿真得以进行,在J1处加载一个系统自带的差分接收端DIN1。并设置相应的工作频率。

图2 MAX3748与J1之间互连的拓扑结构

仿真结果及分析 通过仿真结果分析,信号质量达不到设计的要求,主要有以下问题:(1)上升沿及下降沿存在非线性;(2)波形存在一定的过冲和下冲;(3)边沿速率变慢。针对以上问题,通过对电路进一步的分析发现,这些现象是由于两个方面的因素引起的。1)由于SFP光收发模块主要采用差分线进行信号的传输,根据SFP-MSA协议,主机板上的差分阻抗为100Ω。而且,MAX3748的差分输出端的阻抗为100Ω,在前仿真中,系统提取拓扑结构时,采用默认的阻抗为60Ω的微带线,造成了阻抗不匹配。2)由于在J1后面加载了系统自带的差分输入端,当其处于高阻态时,相当于终端开路的情况,存在较大的反射。

因此,为了确保信号的质量,必须进行阻抗匹配。设置差分传输线的阻抗为100Ω,根据差分微带线的理论,采用传输线计算软件可以计算出差分线的线宽为15mil,线间距为10mil,相应的单端阻抗约为62.5Ω。由于差分线之间存在一定的耦合,将前面仿真的拓扑结构中的无损微带线换成实际的有损及耦合微带线来进行仿真分析。同时,在拓扑结构中加上50Ω的终端电阻接到3.3V电源。

修改后的拓扑结构如图3所示。

图3 修改后的拓扑结构

从仿真波形及眼图分析可知,信号具有比较好的信号完整性。信号的过冲幅度约为54mV,上升沿和下降沿约为100ps左右,差分输出信号的摆幅达到850mV左右,满足信号输出的要求。(陈伟,姚天任,黄秋元,王桂琼)

[1]. PCB datasheet https://www.dzsc.com/datasheet/PCB_1201640.html.

[2]. EMC datasheet https://www.dzsc.com/datasheet/EMC_2342312.html.

[3]. SFP datasheet https://www.dzsc.com/datasheet/SFP_2043396.html.

[4]. MAX3748 datasheet https://www.dzsc.com/datasheet/MAX3748_1016360.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。