本文介绍一种基于复杂可编程逻辑器件CPLD(Complex Programmable Logic Device)使用接触式图像传感器实现的图像采集系统。

1 系统概述

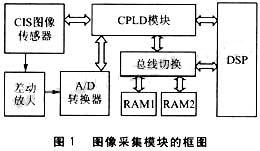

图像采集模块的框图如图1所示,CIS图像传感器在CPL的控制下,将每一个像素的灰度值以模拟电压值的形式通过串行移位方式传输出来,某个像素的电信号再经过差动放大器电路进行信号调理后,由A/D转换器将模拟电压转换数字量,通过总线的切换实现双存储区轮换工作,然后在CPLD的控制下,将转换后的数字信号暂存在存储器RAM中。

CPLD是系统的部件,主要完成CIS图像传感器的时序驱动、A/D转换器的控制、总线切换的控制、地址的产生,数据的存储以及与DSP处理器的协调。

总线切换是采集的关键部分,实现了图像数据存储的两帧轮换结构[2]。当CPLD向存储器RAM1写一帧图像时,DSP向存储器RAM2读取另一帧图像,当存储器RAM1写满且存储器RAM2读完时,由CPLD控制读写总线相互切换,由CPLD继续向存储器RAM2写下一帧图像,DSP向存储器RAM1读取前一帧图像,采用这种两帧轮换的设计方法使得采集和处理可以同时进行,提高了数据采集和处理的效率。

2 硬件构成

2.1 CIS接触式图像传感器

在本文的应用中,接触式图像传感器的有效扫描宽度为216mm。其光电检测单元及柱状透镜分别对应的排成线阵,共有1728个传感单元、能够以红、绿及红外三种光源对图像进行扫描,时钟频率为4M赫兹,型号为C2R2166289。

2.2 A/D转换器

TLC5510是美国TI公司生产的高速模数转换器件[3],它是一种采用CMOS工艺制造的8位高阻抗并行A/D芯片,采样可达20Msps。由于TLC5510不仅具有高速的A/D转换功能,而且带有内部采样保持电路,因此大大简化了外围电路的设计,由于其内部带有标准分压电阻,从而可以从+5V的供电电源中获得2V满刻度的基准电压。

2.3 CPLD及DSP处理器

CPLD芯片选用ALtera公司的MAX7000S系列器件EPM7128SLC84,此芯片可以通过JTAG在线编程,由128个逻辑宏单元和2500个可用逻辑门。在MAX+PLUSⅡ软件中,使用硬件描述语言编程将设计好的硬件逻辑到芯片中,使得对硬件的设计如同软件设计一样方便快捷。

缓冲存储器由2片IS61C1024芯片构成,IS61C1024是8位128KB的高速CMOS静态RAM,存储时间为12ns,能够满足高速数据读写的要求,同时也适合大容量图像数据的暂存。

DSP芯片采用TI公司的TMS320C5402芯片,采用改进的哈佛结构,具有低功耗、高速实时信号处理的特点。

3 CPLD硬件逻辑功能的设计

CPLD是图像采集的部分,它直接控制CIS图像传感器和A/D转换器,完成数字图像数据采集、转换和存储,以及与DSP处理器的握手协调。

CPLD模块总体功能的设计原理如图2所示,CPLD产生CIS图像传感器的时钟信号CLK(4M赫兹),选通信号输入SI,红色光源选通LEDr,绿色光源选通信号LEDg,红外光源选通LEDir。当CPLD控制这几个信号产生相应时序时,CIS传感器通过模拟信号输出引脚SIG向A/D转换器串行移位输出对应像素的灰度。

CPLD控制A/D转换器的输出选通OE信号,使A/D转换器可以输出转换后的数据,同时,CPLD产生数据的存储地址AD[0..16]和写信号WR,将A/D转换器的数字图像数据存储在相应的存储区中。

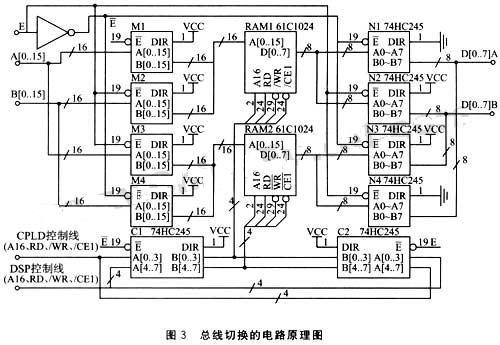

总线切换与双存储区模块实现了两个数据存储区的轮换工作,其原理图如图3所示,CPLD通过控制存储选择信号E来实现双存储区的轮换工作,在上电初始时,选择信号E为高电平,存储区RAM1为写状态,同时RAM2受DSP处理器的控制,改变E的状态,实现总线的切换。

EN、NEXT和READY是DSP与CPLD之间的握手信号,EN为CPLD工作的使能信号,当EN为低电平时CPLD才开始工作。此时,若DSP处理器NEXT端上产生一个脉冲信号,CPLD控制CIS图像传感器采集一行(1728个像素)图像,同时,READY置0,表示正在采集,当一行图像采集完成时,READY信号恢复为高电平,当EN恢复为高电平时,CPLD停止工作,并将选择信号E取反来实现总线切换,将当前存储器由CPLD写状态切换为DSP读状态,实现双存储区的轮换工作。

4 总线切换的实现

在本文的应用中,要求高速实时的进行图像的采集和处理,要求40ms以内就要处理一帧图像,如果采集与存储图像数据占用了太多的时间,则后面的图像处理就无法完成了,为了尽可能缩短采集和存储的时间,在系统中采用了两组存储器进行轮换存储。

在系统中,采用总线切换的方式达到两存储器交替读写的功能,当CPLD将A/D转换器输出的图像数据写入RAM1时,DSP可以读取RAM2中的数据并处理前一帧图像的数据,当CPLD写完一帧图像数据,并且DSP完成前一帧图像的处理后,改为CPLD向RAM2写数据,DSP和CPLD交换存储器,如此循环,使得DSP的图像处理和CIS的图像采集可以并行独立工作,保证了图像的实时和和高速性。

图3中,RAM1和RAM2为2片IS61C1024,构成双数据缓冲存储区,M1-M4分别是由74HC16245所构成的,实现地址总线切换控制,N1-N4是由74HC245所实现的数据总线切换控制,C1和C2实现了存储器控制线(RD读信号、WR写信号等)的切换控制,当选择线E为高电平时,M1、M4、N1、N3及C1处于工作状态,而M2、M3、N2、N4及C2处于高阻状态。因此RAM1的数据总线、地址总线及控制总线只有总线与CPLD相连接,RAM2的全部总线与DSP相连接。从而实现由CPLD向RAM1写数据,DSP从RAM2读数据,当选择线E为低电平时,则情况相反,DSP从RAM1读数据,CPLD向RAM2写数据。

结语

本文依靠接触式图像传感器,采用CPLD与DSP相结合设计实现了适用于实时高速图像处理的图像采集系统。在系统中,采用两帧轮换存储的方式,消除了DSP的等待时间,使采集系统和处理系统可以并行独立工作,采用复杂可编程逻辑器件,使系统集成度高,通用性强,接口简单,并且可以重复编程和系统升级,为实现一个高速实时的图像处理系统提供了基础。

[1]. CPLD datasheet https://www.dzsc.com/datasheet/CPLD_1136600.html.

[2]. CPL datasheet https://www.dzsc.com/datasheet/CPL_2043281.html.

[3]. TLC5510 datasheet https://www.dzsc.com/datasheet/TLC5510_1073963.html.

[4]. MAX7000S datasheet https://www.dzsc.com/datasheet/MAX7000S_1018714.html.

[5]. PLUS datasheet https://www.dzsc.com/datasheet/PLUS_2541182.html.

[6]. IS61C1024 datasheet https://www.dzsc.com/datasheet/IS61C1024_409162.html.

[7]. 12ns datasheet https://www.dzsc.com/datasheet/12ns_2105238.html.

[8]. 74HC245 datasheet https://www.dzsc.com/datasheet/74HC245_1811615.html.

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。