品牌:达泰电子 型号:U*20D 批号:U*2.0 封装:DIP40 营销方式:* 产品性质:* 处理信号:数字信号 制作工艺:半导体集成 导电类型:双*型 集成程度:*规模 规格尺寸:35×55×10mm(mm) 工作温度:0~70(℃) 静态功耗:100(mW)

| 型号:U*20C,U*20D |

关键词:关键词:U*2.0、U*接口、U*总线、U*协议、U*标准、数据采集、U*从设备、U*驱动、U*开发 |

| ■ 简介 |

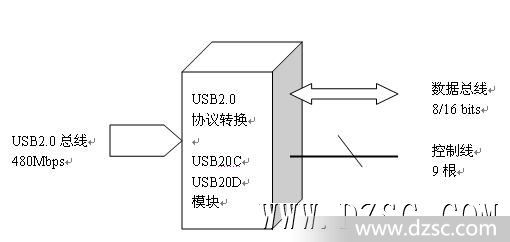

| 对于大多数工程师来说,开发U*2.0 接口产品主要障碍在于:要面对复杂的U*2.0协议、自己编写U*设备的驱动程序、熟悉单片机的编程。这不*要求有相当的VC编程经验、还能够编写U*接口的硬件(固件)程序。所以大多数人放弃了自己开发U*产品。为了将复杂的问题简单化,西安达泰电子*设计了U*2.0协议转换模块。这个模块可以被看作是一个U*2.0协议的转换器,将电脑的U*2.0接口转换为一个透明的并行总线,就象单片机总线一样。从而几天之内就可以完成U*2.0产品的设计。 |  |

| ■ 特 征 | ■ 应 用 |

◎SMT工艺、小体积嵌入式模块

◎提供16位或8位数据总线

◎*U*2.0接口读写速度大于25*/Sec

◎提供*Windows版本驱动程序

◎提供各种高级语言编程源代码

◎提供大量单片机控制实例源代码

◎提供FPGA控制VHDL编程代码

◎模块尺寸:35×55×10mm | ◎便携式U*接口数据采集系统

◎U*逻辑分析仪、U*数字示波器

◎U*接口工业控制产品

◎U*2.0*图像传输 |

■ 订货信息 |

产品型号 | 订货号 | | U*20D | DT_U*20D | | U*20C | DT_U*20C |

|

|

■ U*20C与U*20D的区别 |

U*20C模块是2003年推出的产品,U*20D模块是2006年推出的产品。U*20D模块是在U*20C的基础上,从硬件和软件功能方面进行了改进。U*20D是U*20C的升级产品。二者的功能特点比较如下:

序号 | U*20D模块 | U*20C模块 | | 硬件方面: | 1 | DMA方式时数据总线可选择16位 | DMA方式时数据总线只能是8位 | 2 | 高8位数据线与地址线和控制线复用 | 数据总线没有复用 | 3 | 屏蔽了I2C总线输出 | 开放I2C总线输出 | 4 | 模块尺寸封装没变,与U*20C兼容 | 尺寸与U*20D兼容 | | 软件方面: | 1 | 可以在同一应用程序中控制多个U*20D模块 | 在同一应用程序中只能控制一个U*20D模块 | 2 | 可选16位数据总线进行DMA传输 | 只能8位数据总线DMA传输 | 3 | 提供了FIFO状态查询函数 | 没有FIFO状态查询函数 | | 系统方面: | 1 | DMA读写速度大于25Mbyte/Sec,与电脑速度有关,目前双核计算机测试速度大于30Mbyte/Sec。 | DMA读写速度大于20Mbyte/Sec | 2 | 驱动程序兼容*Windows系统 | 对于有些XP版本驱动可能冲突 |

|

■ 如何使用U*20D快速开发产品? |

选择U*20D模块开发U*2.0接口的从设备是*为快捷简单的途径,对于具有*单片机或FPGA开发经验的设计人员来说,不到一周时间就可以调通U*接口的数*输单元。参考随该产品提供的大量实例代码,并与西安达泰公司技术支持进行沟通开发周期会大大缩短。下面以开发U*2.0接口的数据采集板为例说明过程:

◎ *先根据采样率确定主控芯片:如果A/D采样率小于200KHz,那么采用单片机就可以了;如果如果A/D采样率大于200KHz,建议采用CPLD 、FPGA、ARM、DSP等作为主控芯片。

◎设计硬件电路:把 U*20D模块作为系统硬件的一个单元,主要负责数据的传输。如果希望进行*连续的数*输,那么建议在系统中设计比较大的缓存单元(FIFO、SRAM或双口RAM等)。

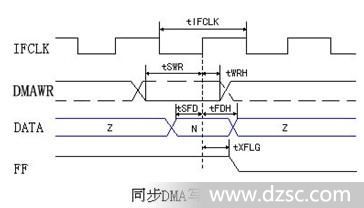

◎编写程序:程序分硬件程序和*机程序两个部分。硬件程序主要协调A/D转换器、存储器和U*接口的控制。对于U*20D模块来说编程就是*简单的事,只要搞清楚DMA的时序就可以了。*机软件程序一般用高级语言编写,例如VC、VB、Delphi,Labview也可以,无论采用那种语言,都是调用U*20D附带的Windows API函数(以U*20D.DLL形式提供)。对于PCI或ISA总线编程熟悉的话,原理都是一样的。 |

■ U*20D模块的DMA模式解释 |

DMA模式是U*20D模块的*大优点,U*2.0接口的*数*输就是通过DMA方式体现的,我们知道U*2.0的接口*大速率为480Mbit/sec,理论字节速度为48Mbyte/Sec。通过用目前双核电脑测试,U*20D模块的DMA*传输速度可以*35Mbyte/Sec。*速度是不包括协议包的数据的,所以比理论速度慢一些,实际上接口速度仍是480Mbit/sec。

|

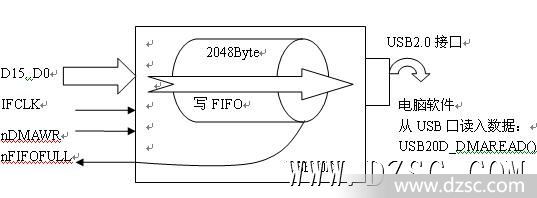

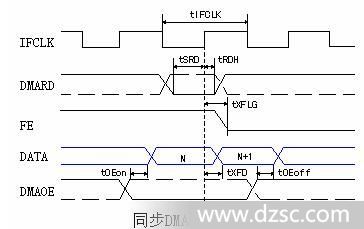

■ 同步DMA写数据FIFO模型及时序图 |

|

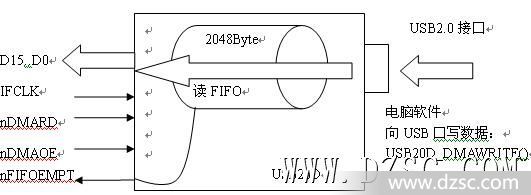

■ 同步DMA读数据FIFO模型及时序图 |

|