PC28F256P30BFE MICRON FLASH存储器 进口原装

地区:广东 深圳

认证:

无

图文详情

产品属性

相关推荐

PC28F256P30BFE

MICRON

BGA

18+

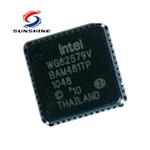

WG82579V INTEL 通信及网络IC 以太网IC 进口原装 QFN48

HCPL-7800-500E AVAGO SOP8 进口 光电耦合器 Optically Isolated Amplifiers 4.5 - 5.5 SV 8 dB

TMS320F28335PGFA TI LQFP176 数字信号处理器和控制器 - DSP, DSC Digital Signal Controller

BLM15BD102SN1D MURATA 村田 铁氧体磁珠和芯片 原装 SMD

SC4215ASTRT Semtech SOP8 低压差稳压器 VRYLW INPT/DRPOUT 2AMP REG W/E

ADN8833ACPZ-R7 ADI 进口原装 LFCSP 电源管理IC 电源管理 PMIC

LTR-553ALS-01 LITEON SMD 进口 光学数位转换器 Ambient Light Photo Sensor

NTF3055-100T1G SOT223 ON 安森美 进口 MOS(场效应管) MOSFET 晶体管

FGA40N65SMDIGBT 晶体管

FAN3224TMX 门驱动器 dual 4A with non-inverting TTL