图文详情

产品属性

相关推荐

NE555DR

NE555DR

NE555DR

FEATURES

DESCRIPTION/ORDERING INFORMATION

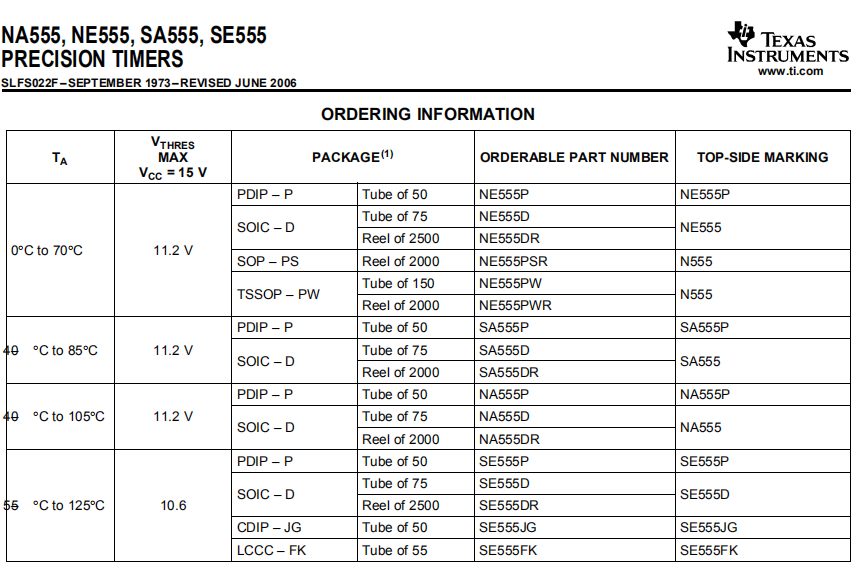

NA555, NE555, SA555, SE555

PRECISION TIMERS

SLFS022F–SEPTEMBER 1973–REVISED JUNE 2006

• Timing From Microseconds to Hours • Adjustable Duty Cycle

• Astable or Monostable Operation • TTL-Compatible Output Can Sink or Source

up to 200 mA

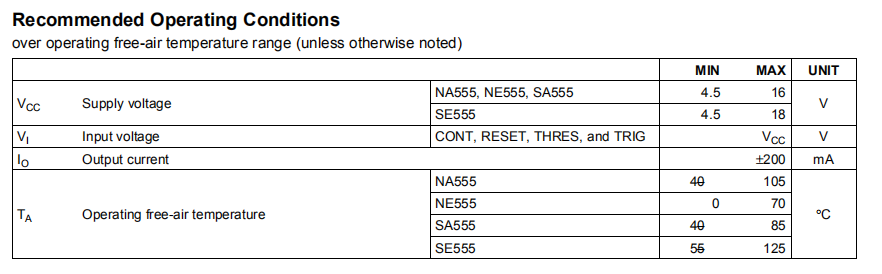

These devices are precision timing circuits capable of producing accurate time delays or oscillation. In the

time-delay or monostable mode of operation, the timed interval is controlled by a single external resistor and

capacitor network. In the astable mode of operation, the frequency and duty cycle can be controlled

independently with two external resistors and a single external capacitor.

The threshold and trigger levels normally are two-thirds and one-third, respectively, of VCC. These levels can be

altered by use of the control-voltage terminal. When the trigger input falls below the trigger level, the flip-flop is

set, and the output goes high. If the trigger input is above the trigger level and the threshold input is above the

threshold level, the flip-flop is reset and the output is low. The reset (RESET) input can override all other inputs

and can be used to initiate a new timing cycle. When RESET goes low, the flip-flop is reset, and the output goes

low. When the output is low, a low-impedance path is provided between discharge (DISCH) and ground.

The output circuit is capable of sinking or sourcing current up to 200 mA. Operation is specified for supplies of

5 V to 15 V. With a 5-V supply, output levels are compatible with TTL inputs.

NE555DR

TI

SOP

黑色

环保

2500/盘

德州

19+