图文详情

产品属性

相关推荐

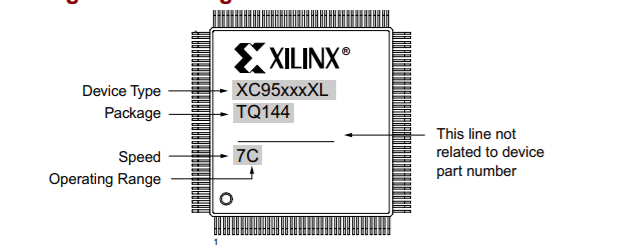

5ns pin-to-pin逻辑延迟•系统频率高达178mhz可编程逻辑XC9572XL-10VQG44C

72个宏孔,1600个可用门•可在小的足迹包- 44脚PLCC(34个用户I/O脚)

- 44引脚VQFP(34个用户I/O引脚)可编程逻辑XC9572XL-10VQG44C

- 48引脚CSP(38个用户I/O引脚)- 64引脚VQFP(52个用户I/O引脚)

- 100引脚TQFP(72个用户I/O引脚)-所有套餐均免费提供可编程逻辑XC9572XL-10VQG44C

•针对高性能3.3V系统进行优化-低功率操作- 5V宽容的I/O引脚接受5V, 3.3V,和2.5V

信号- 3.3V或2.5V输出能力-先进的0.35微米功能尺寸的CMOS

快闪™技术•先进的系统功能——在系统可编程可编程逻辑XC9572XL-10VQG44C

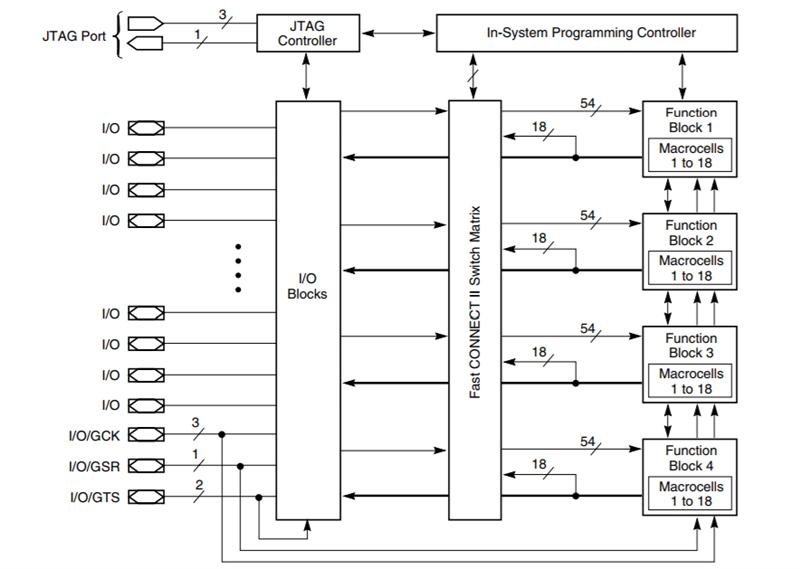

-优越的插销锁定和例行性与快速连接™II开关矩阵-超宽54输入功能块

-每宏单元最多90个产品术语个人product-term分配-本地时钟反转,三个全局和一个product-term时钟

每个输出引脚单独的输出使能-所有用户和边界扫描引脚的输入滞后

输入-所有用户pin输入上的总线保持电路

-完整的IEEE标准1149.1边界扫描(JTAG)快速并发编程

•对单个输出进行旋转速率控制•增强数据安全功能

•卓越的质量和可靠性续航力超过10,000程式/擦除

周期- 20年数据保存

- ESD保护超过2000 v

•pin -兼容5V-core XC9572设备

44针PLCC包装和100针TQFP包装

警告:编程温度范围TA = 0°C到+70°C描述

XC9572XL是3.3V CPLD的高性能目标mance,低压在前沿通信中的应用

阳离子和计算系统。它由四个部分组成54V18功能块,提供1600个可用门

传播延迟为5ns。查看图2了解概述。能力评估在CPLDs中,功耗的变化很大程度上取决于-

对系统的频率、设计应用和输出进行了分析

装载。为了帮助减少功耗,每个宏单元

在XC9500XL设备中可以配置为低功耗

模式(从默认的高性能模式)。在另外

此外,未使用的产品术语和宏细胞是自动的

cally被该软件关闭,以进一步节省电力。对于ICC的一般估计值,可以用下式表示使用:

ICC(mA) = MCHS(0.175*PTHS + 0.345) + MCLP(0.052*PTLP)

+ 0.272) + 0.04 * MCTOG(MCHS +MCLP)* f地点:

高速配置中的宏细胞PTHS =高速乘积项的平均数量

每一个宏单元低功耗配置下的宏细胞PTLP =每项低功率积项的平均数目

宏单元f =最大时钟频率每只钟平均有%的人字拖在开关(~ 12%)

这个计算是根据实验室的测量结果得出的一个XC9500XL的部分充满16位计数器和允许

要启用的单个输出(LSB)。实际的刑事法庭

值随设计应用程序的不同而变化,应该是veri-

在系统正常运行时发生故障。

XC9572XL-10VQG44C

34 I/O

178 MHz

20 mA

VQFP-44