图文详情

产品属性

相关推荐

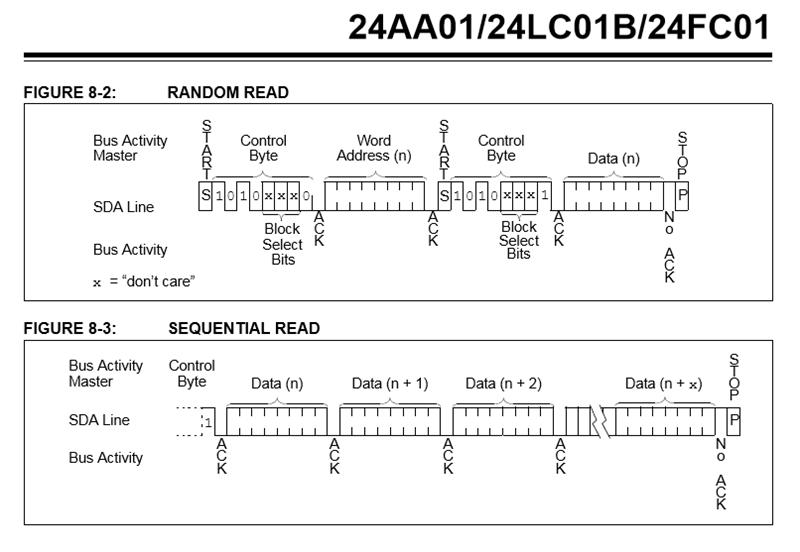

24XX01支持双向、二线总线和数据传输协议。将数据发送到总线的设备定义为发送器,而将接收数据的设备定义为接收器。总线必须由主设备控制,主设备生成串行时钟(SCL),控制总线访问并生成启动和停止条件,而24XX01作为从设备工作。主设备和从设备都可以作为发射机或接收机工作,但是主设备决定激活哪个模式。

定义了以下总线协议:•只有在总线空闲时才可以启动数据传输。•在数据传输过程中,当时钟线高时,数据线必须保持稳定。当时钟线高时,数据线的变化将被解释为启动或停止条件。因此,定义了以下总线条件(图4-1)。4.1总线不繁忙(A)数据线和时钟线保持高电平。4.2开始数据传输(B)当时钟(SCL)高时,SDA线从高到低的转换决定了一个启动条件。所有命令之前都必须有Start条件。4.3停止数据传输(C)当时钟(SCL)高时,SDA线从低到高的转换决定了停止状态。所有操作都必须以Stop条件结束。

4.4数据有效(D)当某一启动条件后,数据线在时钟信号高周期内保持稳定时,数据线状态为有效数据。在时钟信号的低周期内,必须改变线路上的数据。每比特数据有一个时钟脉冲。每个数据传输都使用Start条件启动,并使用Stop条件终止。在开始和停止条件之间传输的数据字节数由主设备决定,理论上是无限的(尽管在执行写操作时只存储后8个字节)。当覆盖发生时,它将基于先进先出(FIFO)原则替换数据。每个接收设备在寻址时,必须在接收到每个字节后生成一个确认。主设备必须产生与此确认位相关联的额外时钟脉冲。

承认装置必须在承认时钟脉冲期间拉下SDA线,使SDA线在与承认相关时钟脉冲的高周期内保持稳定的低电平。此外,设置和保持时间必须考虑在内。在读取期间,主进程必须通过在从进程之外的最后一个字节上不生成确认位来向从进程发出数据结束的信号。在这种情况下,从服务器(24XX01)将保持数据行高,以使主服务器能够生成Stop条件。

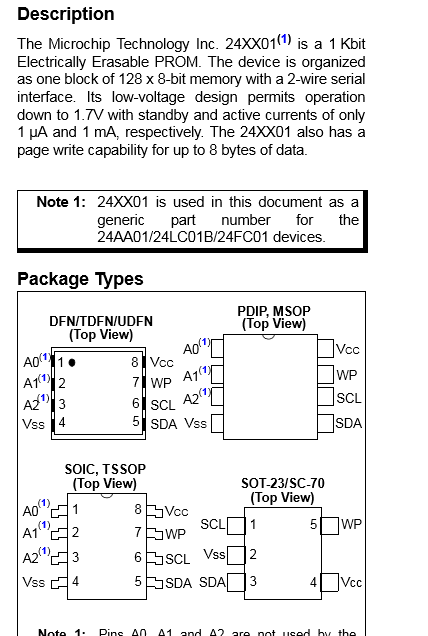

1KBIT

128*8

400khz

3MA

-40-85

SOT23-5