随着通讯速度的提升,出现了很多差分传输接口,以提升性能,降低电源功耗和成本。早期的技术,诸如emitter-coupled

logic(ECL),使用不变的负电源供电,在当时用以提升噪声抑制。随着正电压供电技术发展,诸如TTL和CMOS技术,原先的技术优点开始消失,因为他们需要一些-5.2V或-4.5V的电平。

在这种背景下,ECL转变为positive/pseduo

emitter-coupled logic

(PECL),简化了板级布线,摒弃了负电平供电。PECL要求提供800mV的电压摆幅,并且使用5V对地的电压。LVPECL类似于PECL也就是3.3V供电,其在电源功耗上有着优点。

当越来越多的设计采用以CMOS为基础的技术,新的高速驱动电路开始不断涌现,诸如current

mode logic(CML),votage mode logic(VML),low-voltage differential

signaling(LVDS)。这些不同的接口要求不同的电压摆幅,在一个系统中他们之间的连接也需要不同的电路。

1、直流耦合

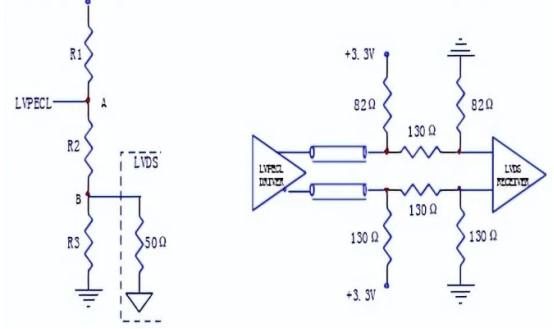

LVPECL到LVDS 的直流耦合结构需要一个电阻网络,如图1.1中所示,设计该网络时有这样几点必须考虑:首先,我们知道当负载是50Ω接到Vcc-2V 时,LVPECL 的输出性能是较优的,因此我们考虑该电阻网络应该与较优负载等效;然后我们还要考虑该电阻网络引入的衰减不应太大,LVPECL 输出信号经衰减后仍能落在LVDS 的有效输入范围内。注意LVDS 的输入差分阻抗为100Ω,或者每个单端到虚拟地为50Ω,该阻抗不提供直流通路,这里意味着LVDS输入交流阻抗与直流阻抗不等.经计算,电阻值为:R1=182Ω,R2=48Ω,R3=48Ω。电阻靠近接收侧放置。

2、交流耦合

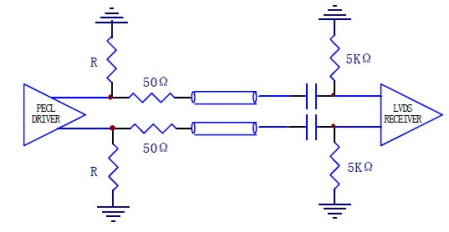

LVPECL 到LVDS 的交流耦合结构如图2 所示,LVPECL 的输出端到地需加直流偏置电阻(142Ω到200Ω),同时信号通道上一定要串接50Ω电阻,以提供一定衰减。LVDS 的输入端到地需加5KΩ电阻,以提供近似0.86V 的共模电压。

在信号转换方面,LVPECL到LVDS的转换则需要考虑衰减电阻和交流耦合电容的放置,以及LVDS接收器的重新偏置。相反,LVDS到LVPECL的转换也需要适当的电路设计和元件选择。