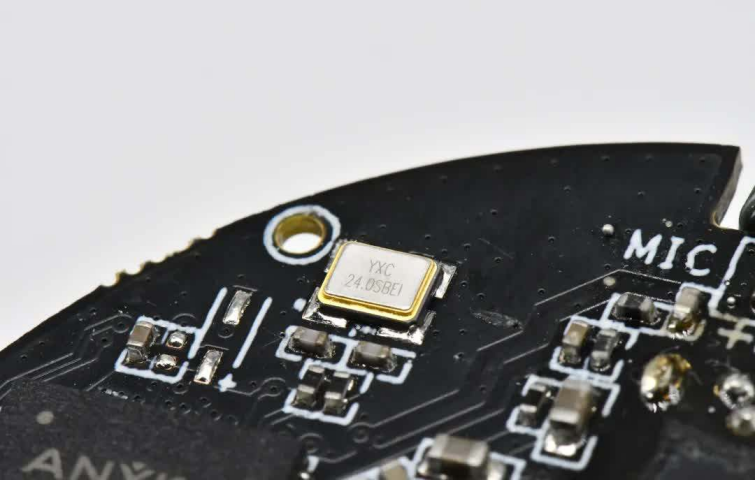

晶振作为时钟电路中必不可少的信号传递者,单片机要想正常运作就需要晶振存在。因此,在电子电路设计中也少不了晶振的参与。一个好的晶振电路设计,是能够为电子提供蕞好的空间利用率,同时发挥蕞大的功能性作用。

振荡原理

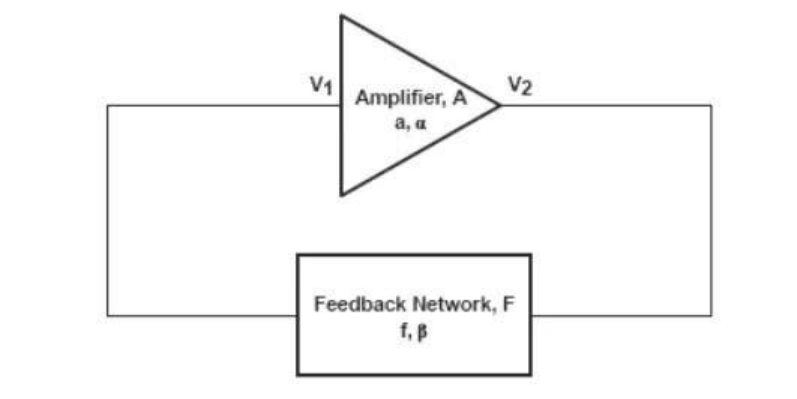

振荡器是一个没有输入信号的带选频网络的正反馈放大器。从能量的角度来说,正弦波振荡器是通过自激方式把直流电能转换为特定频率和幅度的正弦交变能量的电路。对于任何一个带有反馈的放大电路,都可以画成下图所示结构:

▲图1 振荡器

当增益满足∣f∣×∣a∣≥1,且相位条件满足α+β=2πn时,构成正反馈环路,起振条件得以满足。上图即构成一个振荡器。

晶振原理

当在晶体两端加上一定的交变电场,晶片就会产生机械形变,石英晶体振荡器是利用石英晶体的压电效应制的一种谐振器件,若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。同时这个机械形变又会产生相应的交变电压,并且其特征频率下的振幅比其他频率点的振幅大得多。根据这个特点,为了得到低的起振电压和短的起振时间,在晶体两端施加的交变电压的频谱能量应主要集中在晶体的特征频率附近。

▲图2 晶振等效电路

在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振。石英晶体振荡器的等效电路如图2所示。当用石英晶体组成并联谐振电路时,晶体表现为感性,其等效品质因数Q值很高。等效阻抗频率特性如图3所示。

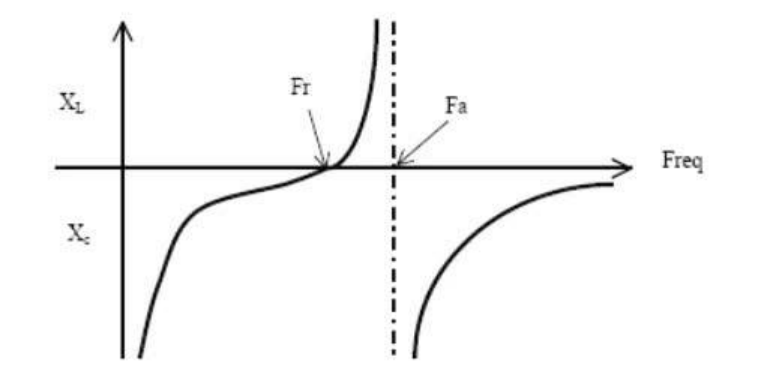

▲图3 晶振等效阻抗

图3中,Fr为串联谐振点。在频率为Fr = 1/(2π√LC)时,图2中串联的L、C谐振,串联支路等效为一个纯电阻。Fa为并联谐振点,此时串联支路等效为电感,与并联的C0谐振,Fa= Fr√1+C/C0。此时等效阻抗趋于无穷大。通常这两个频率点之间的差值很小。

总的来说,可以认为晶振在串联谐振时表现为电阻,在并联谐振时表现为电感。这里建议设计时采用并联谐振。

电工学上这个网络有两个谐振点,以频率的高低分其中较低的频率是串联谐振,较高的频率是并联谐振。

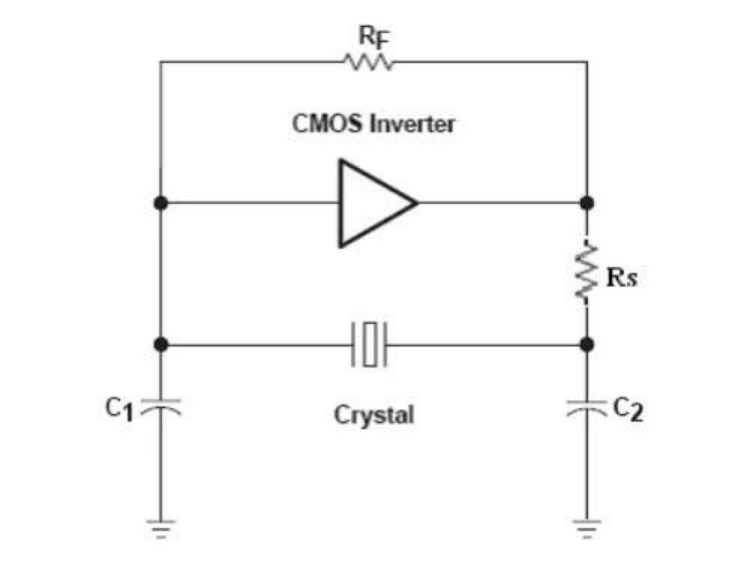

皮尔斯振荡器

倒相器作为放大器,同时提供180度的相移。而晶振及负阻电容作为反馈回路,提供剩下的180度相移。RF为反馈电阻,用来决定倒相器的直流工作点,使之工作在高增益区(线性区)。这个电阻值不能太小,否则会导致环路无法振荡。该电路利用晶振的并联谐振,由于并联谐振与C0有关,会受寄生电容影响,因此增加负载电容C1、C2,可减小C0对谐振频率的影响。同时C1、C2的加入会影响起振时间和振荡频率的准确度。负载电容的选择,应根据晶振供应商提供的datasheet的数值选择。在许可范围内,负载电容值越低越好。容值偏大虽有利于振荡器的稳定,但将会增加起振时间。

▲图4 皮尔斯振荡器电路

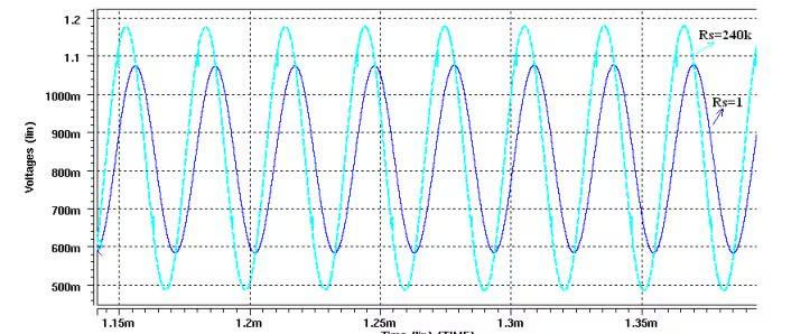

Rs用于抑制高次谐波,从而使振荡器获得较为纯净的频谱。Rs的值若太小的话,可能会导致晶振的过分驱动(overdrive),导致晶振损坏或寿命减短。通常取Rs=XC2。Rs的影响可以由下图看出。

▲图5 Rs的影响(来自参考资料)

电路设计

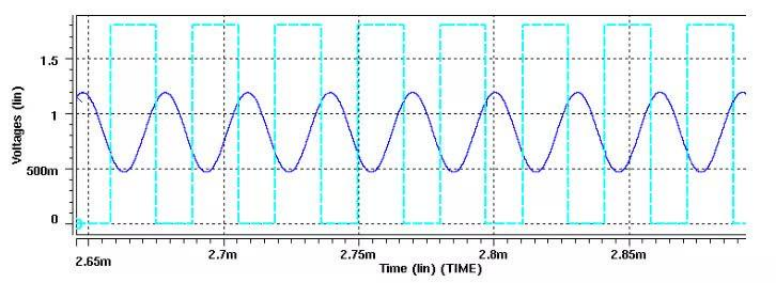

如图6,PM0和NM0构成倒相器,与片外电路共同组成振荡环路。PM7~PM9和NM7~NM9组成施密特触发器,对波形进行整形和放大。输出信号再经过两级倒相器,以提高输出级驱动能力。

▲图6 xtal电路原理图

仿真结果演示

Rs小的时候,在同样的激励电压下,波形幅度比Rs大的情况小很多,导致XC输出为一根直线。

▲XOUT

▲图7 XOUT和XC的波形图

晶振设计注意事项

在低功耗设计中晶体的选择非常重要,尤其带有睡眠唤醒的系统,往往使用低电压以求低功耗。由于低供电电压使提供给晶体的激励功率减少,造成晶体起振很慢或根本就不能起振。这一现象在上电复位时并不特别明显,上电时电路有足够的扰动,很容易建立振荡。在睡眠唤醒时,电路的扰动要比上电时小得多,起振变得很不容易。在振荡回路中,晶体既不能过激励(容易振到高次谐波上)也不能欠激励(不容易起振)。

晶体的选择应考虑以下几个要素:谐振频点、负载电容、激励功率、温度特性、长期稳定性。换句话说,晶振可靠性工作不仅受到负载电容的影响。对于负载电容的选择,应根据晶振供应商提供的datasheet的数值选择。在许可范围内,负载电容值越低越好。容值偏大虽有利于振荡器的稳定,但将会增加起振时间。有的晶振推荐电路甚至需要串联电阻RS,它一般用来来防止晶振被过分驱动。过分驱动晶振会渐渐损耗减少晶振的接触电镀,这将引起频率的上升,造成频率偏移,加速老化。

设计经验总结

01首先要选择一个低的等效串联电阻的晶体。晶体串联电阻低有利于解决起振的问题。因为低的晶体等效阻值有利于增加环路增益。

02通过缩短印制电路板的连线间距来减低寄身电容。从而可以帮助解决起振问题和晶振频率稳定度的问题。

03应该保持对晶振应用温度和电压范围保持监控,从而保持晶体起振频率有必要的话要调整电容电阻的值。

04想要得到蕞佳效果,晶振设计应该采用Vdd峰峰值的至少40%作为驱动时钟反相器的输入信号。仅仅调节晶振两端是不能达到这一要求的。我们也可以参考晶振制造商的使用说明来获得关于晶振设计进一步的帮助。

05对于推荐蕞优化的R1的阻值可以这样得到,首先计算电容C1,C2的值,然后在R1的位置上设置一个电位计,将电位计的初始值设置为XC1。这样可以通过调节电位计来保证在所需要的频率下起振以及维持晶体稳态振荡。