三相电机运行需要三相逆变器,其一般组成为:6个功率晶体管(MOSFETs或IGBTs)、控制晶体管的栅极驱动器(一个或多个)、实现控制算法(速度、转矩控制等)的控制逻辑电路(微控制器或微处理器)。

栅极驱动器为数字控制和功率执行器之间的模拟桥梁,其必须可靠、抗噪声和扰动鲁棒、(保证控制算法和脉宽调制有效),且为保证安全运行,其在非常规条件下或在系统某一部分失效期间需具备保护和安全功能。

引言

STMicroelectronics STDRIVE601为一款针对N沟道功率MOSFET和IGBT的集成三个半桥栅极驱动器的单芯片。该芯片采用了ST公司的BCD6s-高压技术,该技术将双极性、CMOS和DMOS器件与可驱动高侧晶体管且击穿电压超过600V的浮动单元集成在了同一芯片上。新一代的BCD6s技术确保了该器件一流的稳健性。

该器件还具备几项辅助功能和特点,这有助于加速系统设计、减少外围元器件和电路。避免针对噪音和扰动来使用复杂琐碎的保护电路且可确保整个应用简单经济。

STDRIVE601采用小体积的SO28封装,可替代三个半桥驱动器以简化PCB板布局。6路输出均可实现350mA灌电流和200mA拉电流,且栅极驱动电压范围为9-20V。

三个高侧自举单元工作电压高达600V且可由内置自举二极管供电,可节省PCB面积并减少元件数量。低侧和每个高侧驱动单元的欠压锁定(UVLO)功能可防止功率开关工作在低效或危险状态。

由于技术发展和设计优化,STDRIVE601可在负压尖峰超过100V时保证稳健性,并且以业界的85ns响应逻辑输入。高低侧单元的延时匹配消除了周期畸变且可保证高频运行,互锁和死区插入同时也避免了未知情况下的交叉导通。

智能关断电路确保了有效的过流保护,高速保护功能可在检测到过载或短路后的短短360ns内关断栅极驱动器。设计者可通过改变外部电容的容值来设置和调整保护关断时间而不会影响芯片关断反应时间,该芯片还提供了一个低电平有效故障指示引脚。

ST公司还提供了EVALSTDRIVE601评估板以帮助用户探索STDRIVE601的功能并迅速启动和运行个原型。

负压现象

半桥输出中的负压尖峰在功率应用中非常常见,特别是空间或机械限制导致无法对PCB布局进行优化时。负压尖峰会导致一些不良现象,如自举电容的过充电以及器件稳健性不足时输出侧的误动作。

在半桥拓扑结构中,特别是驱动大感性负载时,功率半桥的输出很容易出现负压,表现为初始的动态尖峰和后续的静态负压(如图1-b所示)。这个现象出现在桥臂硬开关切换至低电平输出且负载电流由桥臂输出至负载时。当高侧开关关闭时,感性负载元件试图维持输出电流恒定。输出电压逐渐降低且当其降低至“地”电平值时,电流开始经低侧续流二极管续流,该二极管正向导通。动态负压主要是由于与半桥低侧电流路径续流二极管串联的PCB板子上寄生电感引起的高dI/dt而造成的尖峰。另外,动态负压还与低侧续流二极管的正向尖峰电压(其在短暂时间内由高压反向状态切换到正向导通状态)和分流电阻的寄生电感有关。

静态负压主要由采样电阻(如果有)的电压降和续流二极管的正向电压降组成(如图1-a)。

图1半桥电路的负压现象

栅极驱动器稳健性

STDRIVE601设计的主要特点是其对噪音、扰动和负压现象出色的稳健性。得益于创新的电平转换器架构和ST先进的制造工艺技术,该驱动器具有出色的抗击高负压尖峰能力,并且能够在非常陡峭的共模暂态下正常运行。

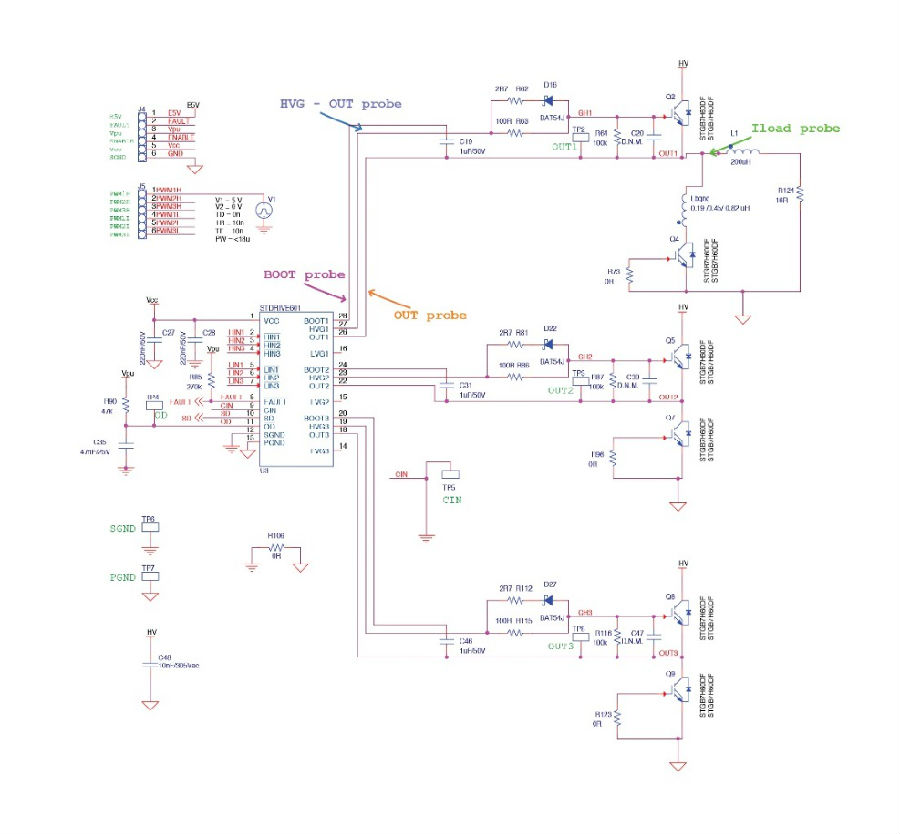

在专用的测试电路(图2)中测试并确认了该芯片对负压尖峰的抗扰性,该设计旨在人为地产生比实际应用中发现的尖峰大得多的负压尖峰。

图2中RL负载为200 H、16 Ω,且为了模拟PCB布局较差时引入的杂散电感的影响,选了几个电感(0.19 H, 0.45 H, 0.82 H)可与低侧IGBT串联。

图2负压现象分析电路

图3为杂散电感为0.82 ?H时的现象:输出由300V摆动至0V,负压尖峰峰值为-127V且保持148ns。经过几次的切换,没有任何损坏或者运转失常。

图3 杂散电感为0.82 H时通道1输出存在-127V负压尖峰

自举二极管

STDRIVE601内部自举二极管采用额定600V MOSFETs实现,其在LVG输出打开时经由主电源(VCC)给每个通道的自举电容充电。这避免了使用大且贵的外部高压二极管。

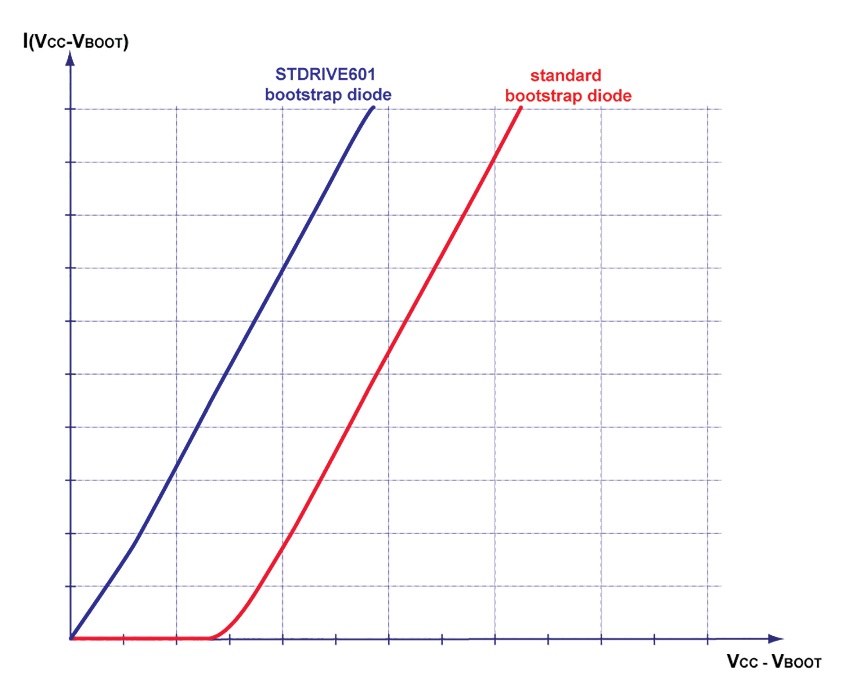

图4 STDRIVE601自举二极管和传统自举二极管对比

内置自举电路导通,有一个正向偏置,不存在实际二极管中的偏置电压。图4展示了这两者的区别,其表示了STDRIVE601自举二极管和传统自举二极管的I-V(电流-电压)转移曲线。对于给定电流,这一特征在剩余电压降方面优势突出,且可在电压降较小时也可对自举电容进行充电,而传统二极管对此稍显乏力。

过流智能关断保护

STDRIVE601内置了一个比较器,该比较器通过智能关断(SmartSD)电路进行故障保护。

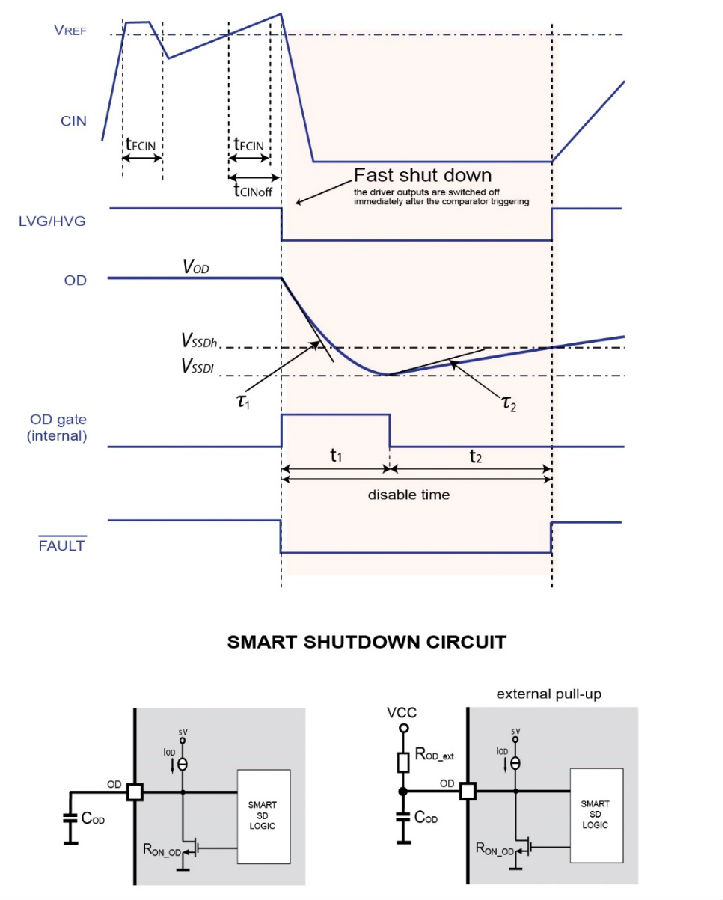

SmartSD电路可在过载或过流时关断栅极驱动器,且故障检测至实际输出关断之间的延时仅360ns。保护干预时间与故障后的禁用时间相互独立,且保护响应速度为市场上其他栅极驱动器的两倍。这允许设计者在不增加内部保护延迟时间的情况下,将故障事件后输出的禁用时间增加到非常大的值。禁用时间取决于外部电容COD的容值和可选的连接到OD引脚的上拉电阻的阻值(见图5)。

用于智能关断的比较器具有一个内部参考电压VREF且其连接到反相输入端,同相输入端连接至引脚CIN。比较器的CIN引脚可连接至外部分流电阻,进而实现简单快速的过流保护功能。比较器输出信号经滤波后输入到SmartSD逻辑单元,其滤波时间为固定时间tFCIN(约300ns)。

VREF阈值典型值为460 mV,比较器输入(CIN)滞环电压约为70 mV。当CIN引脚上脉冲电压高于VREF时,SmartSD逻辑被触发并立即将驱动器输出置低(OFF)。同时,故障引脚(FAULT)强制置低来指示该事件(例如输入到微控制器)且OD开始让外部电容COD放电以设置故障事件的输出禁用时间。一旦输出禁用时间到期,FAULT引脚将释放且驱动器输出重新跟随输入引脚。

总禁用时间由如下两部分组成:

· OD解锁时间(图5中t1),即电容COD放电至VSSDl阈值的时间。SmartSD比较器被触发时放电立即开始。

· OD重启时间(图5中t2),即电容COD重新充电至VSSDh阈值的时间。当OD上电压达到VSSDl,故障状态清除(CIN < VREF - CINhyst),OD内部MOSFET关闭,此时COD重新充电。这个时间是禁用时间的主要组成部分。

当OD未经外部上拉时,外部电容COD放电时间常数取决于COD和内部MOSFET的特性(如下方程(1)所示),重启时间取决于内部电流源IOD和电容COD(如下方程(2)所示)

(1)

(2)

其中为OD浮动电压。

当OD经外部上拉电阻ROD_ext连接至VCC时,OD放电时间取决于外部网络ROD_ext、COD和内部MOSFET的电阻RON_OD(如下方程(3)所示),重启时间取决于流过ROD_ext的电流(如下方程(4)所示)。

(3)

(4)

其中,。

图5智能关断时序图

下图为两种不同的电容连接至OD引脚时智能关断功能运行示例。CIN引脚上的触发脉冲宽度为500ns、峰峰值为1V,且内部电流源(IOD)对外部电容进行充电。

= 2.2 F

= 4 V

= 0.56 V

6 A

= 15 V

禁用时间 = 1.46 s

= 330 nF

= 4 V

= 0.56 V

6 A

= 15 V

禁用时间 = 220 ms

图6左图中COD = 2.2F,右图中COD = 330 nF

其它功能和特点

STDRIVE601具有快速和准确的传播延迟。高低侧驱动器从输入翻转到输出开通或关断的延时均为85ns,匹配时间低于30ns且其典型值为0ns。

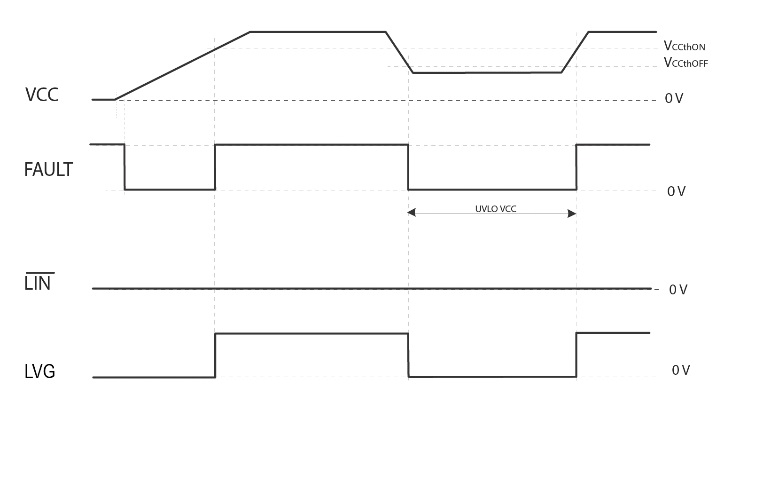

欠压锁定(UVLO)机制监控驱动器供电电压的输出变化,并在该电压降低至低于预设阈值时将输出关断。该保护可防止驱动器在电源电压较低时驱动功率管(这将导致导通损耗过高甚至损坏功率管)。

UVLO阈值具有滞回特性且内置滤波器可防止电源电压上噪音引入不必要的动作。STDRIVE601的6个驱动器均由UVLO机制进行保护。

图7VCC电源上的UVLO机制

总结

三相电机由于具备多项优势,正迅速替代简单的单相和有刷电机。三相驱动器(如三相600V单芯片栅极驱动器STDRIVE601)的易用性、可用性和经济性是这一发展的主要原因所在。STDRIVE601具有稳健性、简单性和节省成本的特点,同时可确保系统受保护并提供安全功能。