供应S70KS1282GABHB020集成电路 存储器

地区:广东 深圳

认证:

无

图文详情

产品属性

相关推荐

S70KS1282GABHB020

CYPRESS

VBGA-24

23+

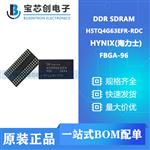

供应 H5TQ4G63EFR-RDC FBGA-96 HYNIX DDR SDRAM

全新原装 S70GL02GS11FHI010 Infineon MRAM磁性随机存储器

供应MT41K128M16JT-125AAT:K FBGA MICRON

供应 IS61WV204816BLL-10BLI BGA-48 ISSI 静态随机存取存储器

全新原装 FM24V02A-GTR Infineon FRAM存储器

全新原装 FM24CL64B-GTR Infineon FRAM存储器

全新原装 CY15E064Q-SXET Infineon MRAM磁性随机存储器

MT41K256M16TW-107 IT:P 原装现货6K

Renesas 70V9289L9PFGI 存储器

MR45V256AMAZAAT-L Rohm FRAM