当设计需要辅助电压轨并且相关电流负载适中时,电容器泵电压倍增器通常是简单、且有效的制造方法。 用您独特的设计让工程界惊叹: 设计理念提交指南 其中简单的是二极管泵倍压器。它仅由两个二极管和两个电容器组成,但具有固有的缺点,即需要单独来源的方波进行驱动,并产生至少两个二极管压降小于电源轨两倍的输出电压。需要有源开关(通常使用 CMOS FET)来避免这种低效率并准确地将电源加倍。 CMOS 倍压器芯片是现成的。Maxim MAX1682 就是一个例子。它适用于当前负载不太重的应用,但它(和类似设备)并不是特别便宜。考虑到通用 CMOS 开关芯片(如 74AC14)的单片售价为 50 美分,1682 单片的成本接近 4 美元,这让我们很想看看是否可以做得更好。 这样做的计划从图 1开始,显示了 CMOS 逻辑反相器的简化草图。

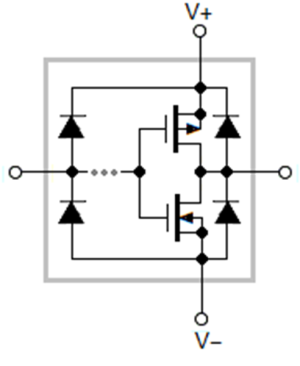

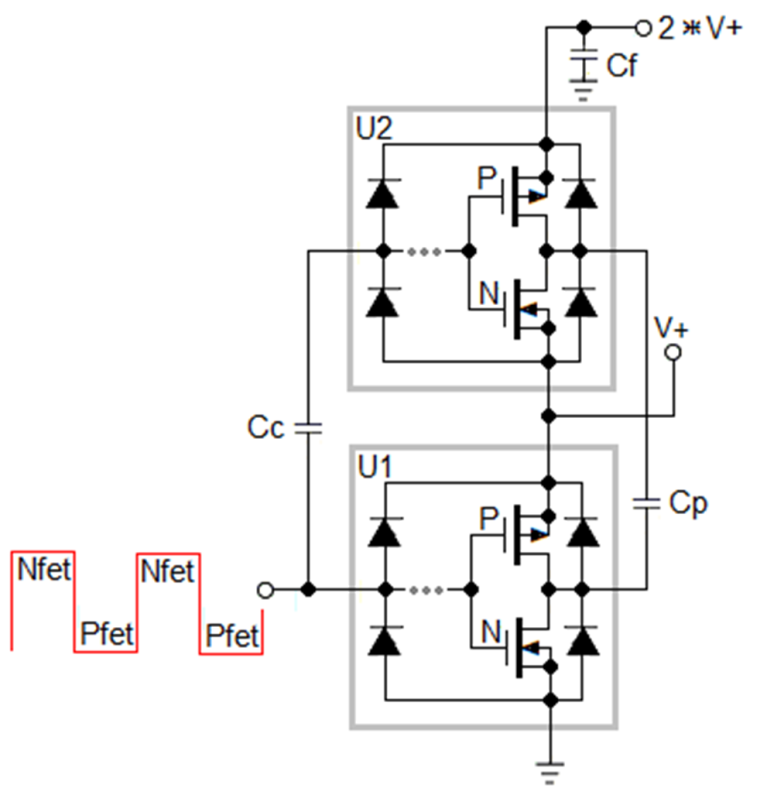

图 1典型基本 CMOS 栅极 I/O 电路的简化示意图,显示钳位二极管和互补 FET 开关对。 注意输入和输出钳位二极管。这些由制造商放置在那里,以保护芯片免受 ESD 损坏,但二极管就是二极管,因此也可以执行其他有用的功能。同样,P 沟道 FET 对旨在在输出逻辑“1”时将 V+ 轨连接到输出引脚,在输出逻辑“1”时将 N 沟道连接到 V- 到引脚。但 CMOS FET 愿意在任一方向传导电流。因此,从引脚流向电源轨的电流与从电源轨流向引脚的电流效果相同。

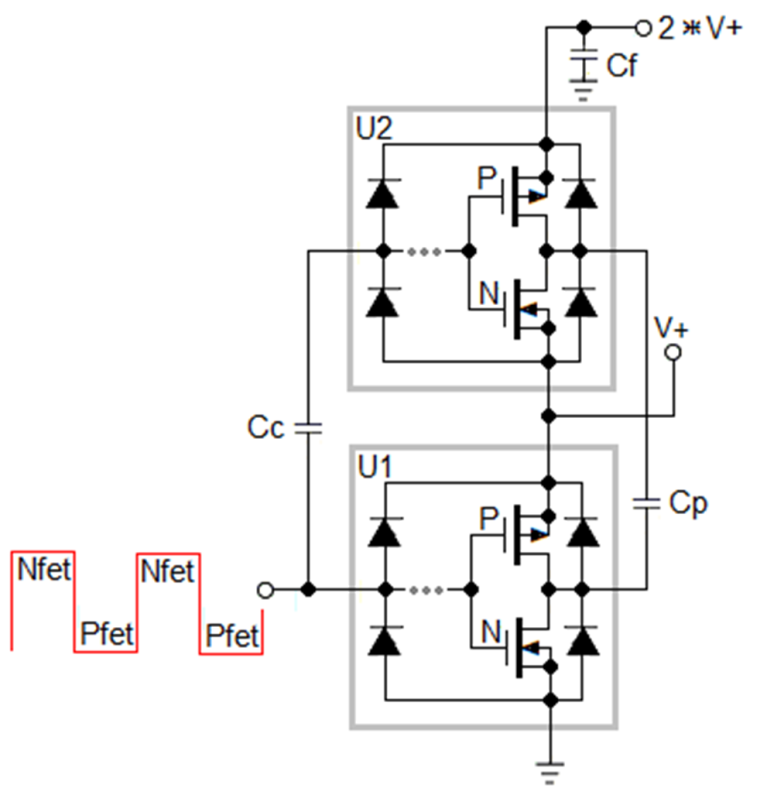

图 2显示了这些基本事实与电荷泵和电压倍增的关系。 图 2简化的倍压器,显示驱动器器件 (U1)、换向器件 (U2) 以及耦合 (Cc)、泵 (Cp) 和滤波器 (Cf) 电容器。 Imagine two inverters interconnected as shown in Figure 2 with a square-wave control signal coupled dire想象一下,如图2所示,两个逆变器相互连接,方波控制信号直接耦合到U1的输入端,并通过直流阻塞帽Cc耦合到U2,U2的输入箝位提供直流恢复。 考虑一下方波的一个半周期。U1和U2的N沟道FET都将导通,将Cp的U2端连接到V+,将U1端连接到地,从而将Cp充电到V+。注意,由于Cp驱动引脚为负,U2输出引脚的电流极性相反。 现在考虑一下当控制信号反转为零时会发生什么。 P FET 将导通,而 N FET 将关闭。这迫使之前由 Cc 接受的电荷通过 U2 的输出和 V+ 引脚转储到 Cf,从而完成电荷泵循环,将一定量的正电荷沉积在 Cf 上。请注意,再次出现流过 U2 的反向电流。该循环随着控制信号的下交替而重复,依此类推。 在启动期间,直到 Cf 上积聚足够的电压以供 U2 内部电路和 FET 栅极驱动正常运行之前,U2 钳位二极管用于整流 Cp 驱动信号并开始对 Cf 充电,直到 FET 可以接管。 理论就讲这么多。将图 2 转换为完整的倍压器如图 3所示。

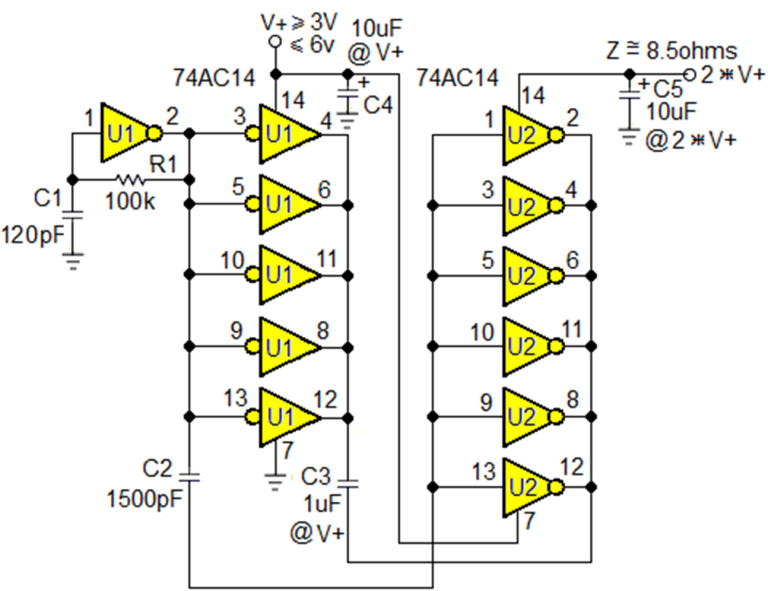

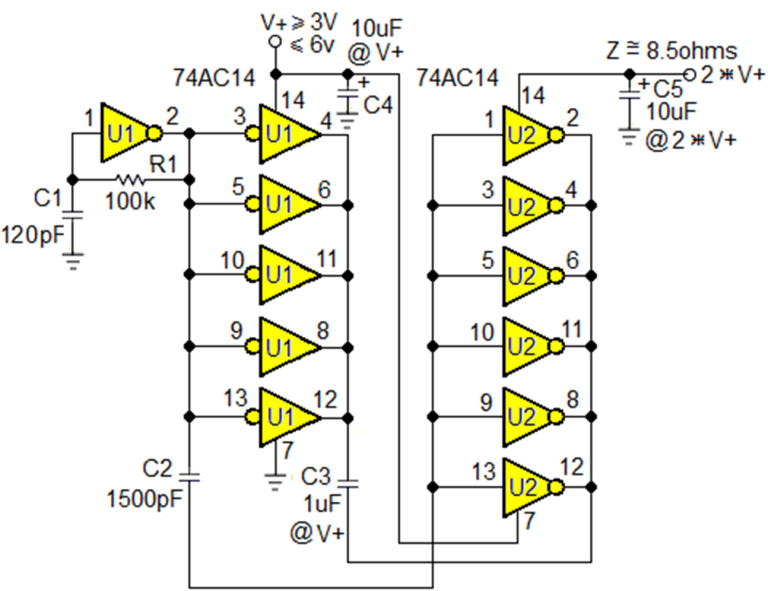

图 3完整的倍压器:由 R1C1、施密特触发器、驱动器 (U1) 和换向器 (U2) 设置的 100 kHz 泵时钟 74AC14 施密特触发器 U1 的引脚 2 上输出 100 kHz 泵时钟。该信号被路由至 U1 的其余 5 个栅极和(通过耦合电容 C2)U2 的 6 个栅极。正电荷通过 C3 转移到 U2,并从那里累积在过滤器帽 C5 上。 尽管 U2 并不真正需要施密特磁滞,但还是为其选择了另一个 AC14,以追求匹配的开关延迟时间,从而提高电荷传输的效率促进同步性。一些性能规格 (V+ = 5V) 包括: 10V输出阻抗:8.5Ω 连续负载:50 mA 50 mA 负载时的效率:92% 25 mA 负载时的效率:95% 空载功耗:440 W 启动时间 < 1 毫秒 那么,如果仅仅将 V+ 加倍还不够的话会发生什么呢?如图4所示,该设计可以轻松级联以形成高效的电压三倍器。扩展到更高的倍数也是可能的。

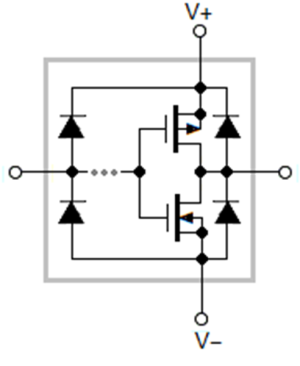

图 4添加四个廉价部件足以使电源电压增加三倍。