另一种获得高GB运算放大器的方法是将一个高增益、低频运算放大器和一个低增量、简频运算放大器并联应用,以获得一个高GB的运算放大器。

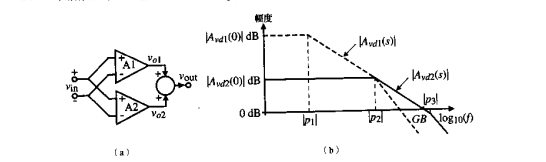

这个概念如图 7.2-14所示。[7]。思路是用低频运算放大器实现低频时的高增益。但是,这个运算放大器具有高阶极点, 这将使得放大器为有条件稳定。一个运算放大器的有条件稳定是指在某些反馈值时反馈放大器不稳定。这经常发生在小的闭环增益的时候。低增益放大器用来扩展高增益运算放大器第二极点((p)上方的斜率为-20dB/十倍频。结果产生一个主极点在、p、GB 为|p|和|A(0)A(0)|乘积的运算放大器。幅度Ax=1(0/dB|Awel(s)|vAI|Aa(s)|YoutA(0)|dBYin|P3|A2vo20dB-GBP2|log10(f)P1|(b)(a)图7.2-14 (a)用并联放大器方法实现高GB;(b)(a)所对应的幅频响应

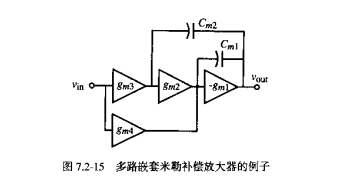

为了正确使用这种技术,两个放大器增益的符号应当是相同的,即同时为正或同时为负。如果不同,就会在右半平面出现零点, 并影响稳定性。图7.2-15更详细地给出了如何使用三级放大器实现这个想法。这一技术称为多路嵌套米勒补偿[7]。通过两路相加产生左平面零点来抵消高增益路径的第二个高阶极点,使-20dB/十倍频斜率延伸到低增益路径的第二个高阶极点。需要注意的是,米勒补偿产生的右半平面零点得以抵消, 且极零点对不会产生慢的时间常数问题。对于感兴趣的读者, 用于图7.2-15 的分析公式和其他结构在Eschauzier 和 Huijsing 文中[7]有详细论述。

这一节给出了一些扩展运算放大器频率响应的方法。在所有的放大器中,频率响应都受到单位增益带宽的限制。在绝大多数的 MOSFET运算放大器中,单位增益带宽是用输入跨导和产生主极点的电容的比值给出的。采用CMOS 技术来获得超过100 MHz的单位增益带宽是很困难的。在许多应用中,运算放大器用负反馈来实现低增益放大器。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。