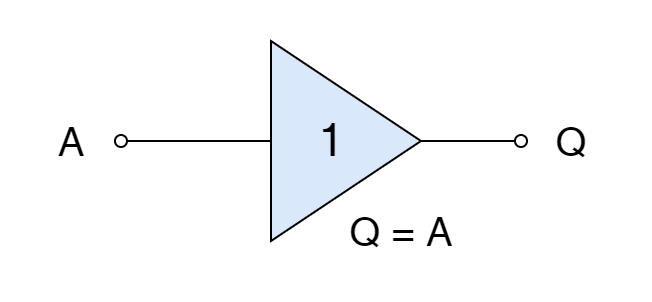

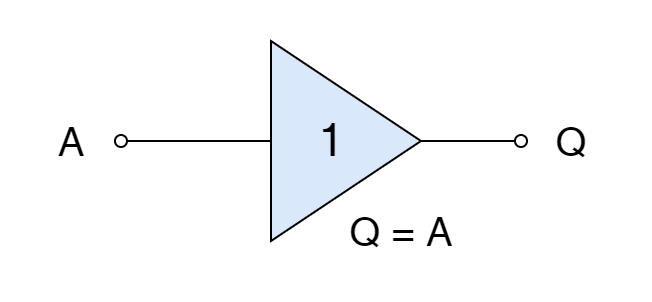

收发器是一种允许总线之间进行双向接口以进行数字或模拟信号通信的设备,并且具有输入和输出控制功能。它使用背对背三态缓冲区通过公共数据总线进行多个设备的通信。与数字缓冲器相反,三态缓冲器允许双向通信并且能够通过使用额外的“启用”输入来控制其输出。在单向接口中,设备可以发送或接收,因此,需要额外的单向接口来用于发送或接收目的。双向接口允许设备发送和接收。“收发器”一词是来自发射器和接收器的两个词的组合。收发器通常也称为驱动器/接收器或发送/接收设备。正如数字缓冲器文章中所讨论的,与其他逻辑门不同,数字缓冲器不在逻辑电路中执行反转或决策。它输出其输入处存在的任何内容,而不对逻辑状态进行任何修改。 数字缓冲器 下图显示了数字缓冲区以及布尔表达式。

图 1:数字缓冲器符号 它是一个单向设备,因此允许输入到输出,即从“A”到“Q”。从布尔表达式可以看出,当输入“A”处于逻辑“高”或“1”时,输出“Q”处于逻辑“高”或“1”,同样,当输入“A”处于逻辑“高”或“1”时,输出“Q”处于逻辑“高”或“1”。逻辑“低”或“0”,输出“Q”处于逻辑“低”或“0”。所示模式适用于正逻辑器件,例如 74HC4050 CMOS 六角缓冲门。缓冲器用于将其他设备或电路彼此隔离/分离,以防止影响彼此的功能或阻抗。此外,缓冲器用作高电流负载的驱动器,如晶体管,因为其扇出(输出驱动)能力与其输入信号相比非常高。例如,微控制器的输出端口设置为处理 25mA 的电流,缓冲器是将敏感微控制器与高压输出电路隔离和/或提供高电流的常见解决方案。开路集电极六角缓冲器/驱动器可用于此目的,例如具有 30V 输出额定值的TTL 74LS07 。下图中显示了 74LS07 的内部电路。

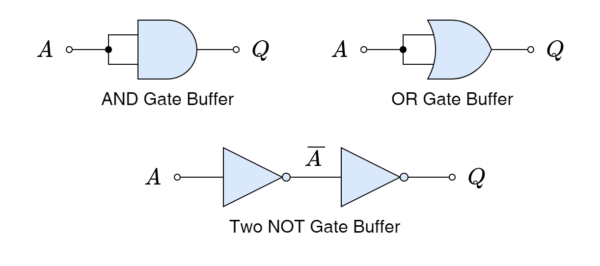

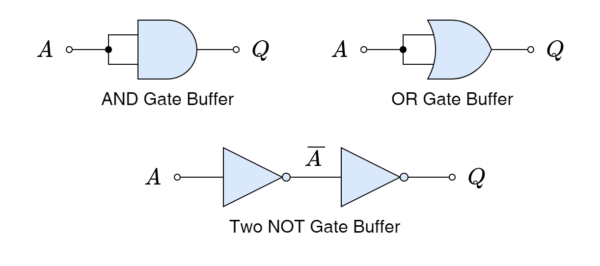

图 2:TTL 74LS07 十六进制数字缓冲器 其他缓冲器设计 还可以使用可用的基本/标准逻辑门(例如“或”、“与”或“非”门)构建数字非反相缓冲器。下图显示了实现该非反相缓冲器的简单组合。

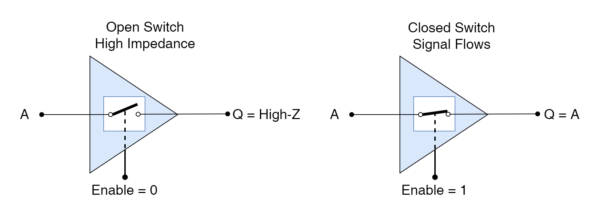

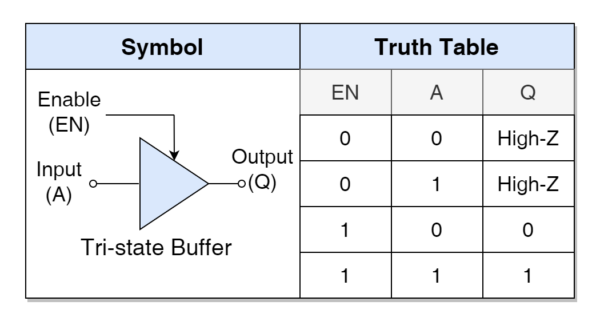

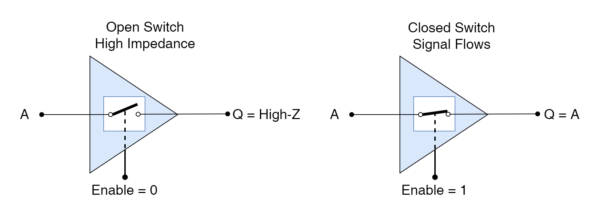

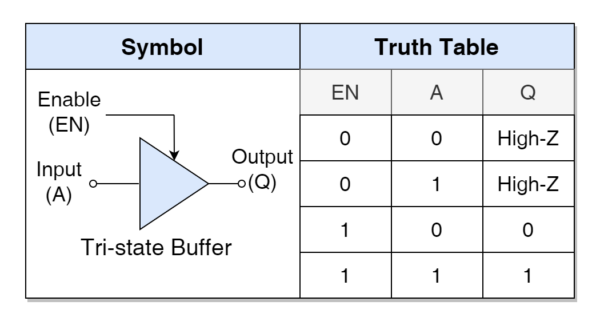

图 3:数字缓冲器等效门 除了数字缓冲器的上述优点之外,其功能还存在一个主要限制,因为其输出始终连接到其输入,这可能会影响输出电路。此外,它限制了控制和减少电路方面的灵活性。这些问题可以通过使用输出端具有三个 (03) 不同状态的三态缓冲器来解决。 三态缓冲器 顾名思义,它是一种具有三种 (tri) 输出状态的缓冲区。三态缓冲器的这三种输出状态是通过不同的输入组合来实现的,为此,与传统的数字缓冲器相比,三态缓冲器使用了额外的输入。该附加输入是启用缓冲器功能的控制输入,称为“启用”(EN) 输入。使用此附加输入 (EN) 有助于实现第三级高阻抗 ( High-Z ),从而隔离或打开输入与输出之间的电路。因此,三态缓冲器具有三种状态,即“OFF”、“ON”和“High-Z”。控制或使能输入可以在逻辑“0”或逻辑“1”时有效,三态缓冲器的输出可以是同相或反相,这一切都取决于 IC 封装。常用和可用的三态缓冲器 IC 是 TTL 74LC125和74LS126。 三态缓冲器开关等效 下图显示了三态缓冲器在开关模式下的等效电路。三态缓冲器的符号与传统的数字缓冲器类似,但具有额外的控制/使能(EN)输入。

图 4:三态缓冲器开关类比 当“启用”输入处于逻辑“1”时,则启用缓冲器功能,并且三态缓冲器将充当常规输入。如果“A”输入为逻辑“0”,则“Q”输出也将为“0”。类似地,当“A”输入变为逻辑“1”时,“Q”变为逻辑“1”。然而,当“启用”输入设置为逻辑“0”时,缓冲器的功能将关闭,并且输出既不是逻辑“0”也不是逻辑“1”。输出进入高阻抗 (High-Z) 状态,表示开路状态并隔离/分离输入“A”和输出“Q”。“A”输入中存在的任何内容都不会反映在“Q”输出中。从上图可以看出,三态缓冲器具有三种状态:逻辑“0”、逻辑“1”和“高阻”,具体取决于“A”和“启用”输入。由于这三种状态,它被称为三态缓冲器。在第三个“高阻”状态下,它以电子方式隔离输入“A”和输出“Q”。此外,在此状态下,输出既不是逻辑“0”也不是逻辑“1”。简而言之:当“启用”输入设置为“0”或“低”状态时,缓冲器的输出变为开路或进入高阻抗(高阻抗)状态。当“启用”输入设置为“1”或“高”状态时,缓冲器将输入信号直接传递到输出。上述功能基于正使能(高电平有效)三态缓冲器,并且在负使能或低电平有效使能输入的情况下相反。积极启用的三态缓冲器的上述功能可以用真值表形式表示,如下所示:

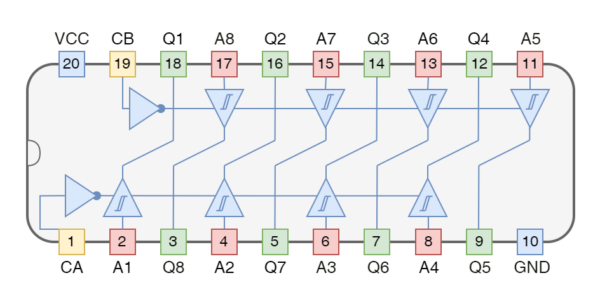

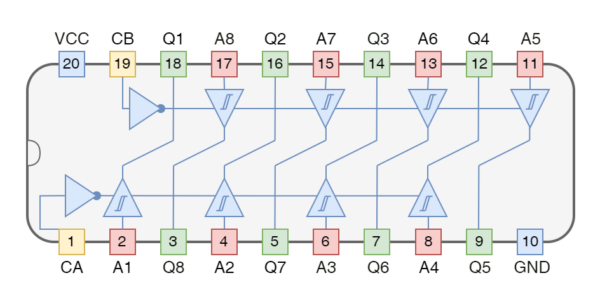

图 5:三态缓冲器符号和真值表 在商业上,三态缓冲器可采用具有四路、六路或八路三态缓冲器/驱动器的 IC 封装。下图所示为 TTL 74LS244八路三态缓冲器的内部电路。

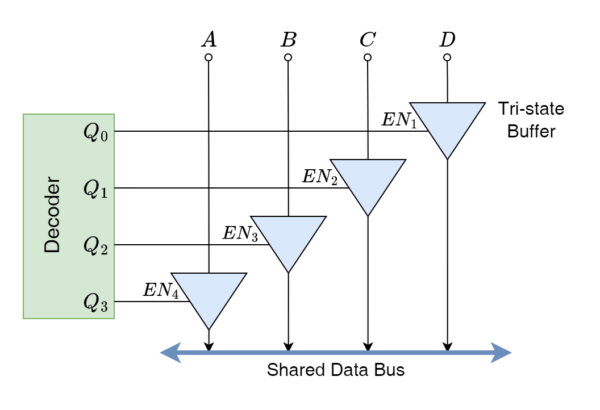

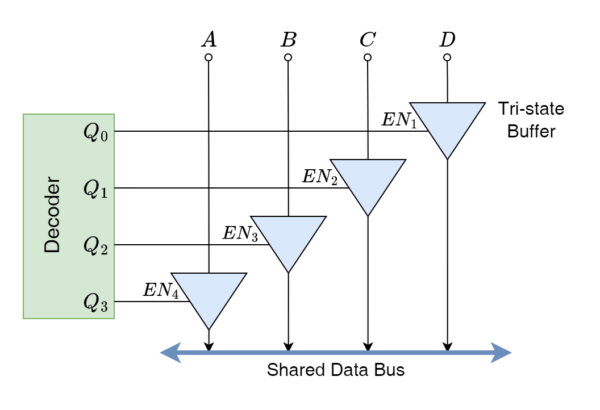

图 6:TTL 74LS244 三态八路缓冲器 上述 74LS244 的八进制三态缓冲器/驱动器分为两组,每组四个(04)缓冲器,每组都有自己的使能输入。在组中,使用公共使能引脚“CA”分别将 A1 至 A4 的输入控制为 Q1 至 Q4 的输出。而使能引脚“CB”控制其余四个带有输入(A4 至 A5)和输出(Q5 至 Q8)的三态缓冲器。 具有多个三态缓冲器的单总线 三态缓冲器的第三状态(高阻)有助于将多个设备连接到单个/公共总线。由于这种高阻抗状态,隔离了输入和输出,这有助于通过禁用相关的三态缓冲器来将不需要的设备与公共总线隔离,并且启用其中一个,以从所需的设备向总线传输数据。在下图中,解码器用于选择四个设备之一,以与公共/共享数据或总线连接。

图 7:三态缓冲器控制的数据总线通信 这些设备通过三态缓冲器与公共/共享数据总线或电线连接,而每个三态缓冲器的控制是使用2位解码器设备来管理的。使用解码器有助于将控制线从四根 (04) 减少到两根 (02)。此外,通过使用解码器,只有一个输出将被设置为“1”或“高”,避免了由于多个设备同时通信而造成的中断。使用此解码器,通过设置相关的三态缓冲器,其中一个设备将被允许与共享/公共总线通信,而其他设备由于其禁用的三态缓冲器而保持隔离。所描述的组合逻辑电路类似于 4 至 1 线多路复用器,因为使用选择线将四条数据线传递到单个输出。因此,使用解码器和三态缓冲器,可以构建多路复用器电路。根据所使用的三态缓冲器的类型,通过将其“启用”输入连接到“Vcc”或“接地”,可以将三态缓冲器转换为传统的数字缓冲器。这样,三态缓冲器将启用,将输入“A”处的任何信号传递到输出“Q”,就像传统的数字缓冲器一样。 双向缓冲控制 上述三态缓冲器使得数据只能从输入“A”传递到输出“Q”,但不能反向传递。为了能够从两侧进行数据传输,就像收发器一样,两个三态缓冲器与一个非门以反向并行方式放置,以反转“启用”输入之一。在下图中,显示了一个双向缓冲区来演示基本结构和工作原理。

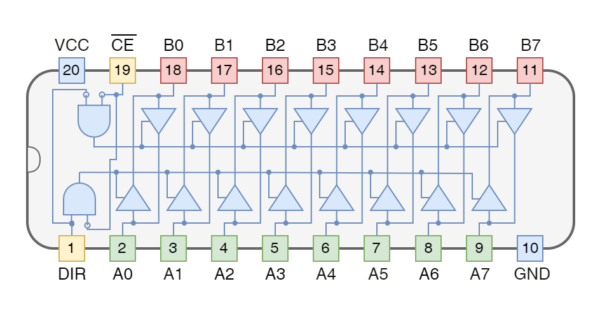

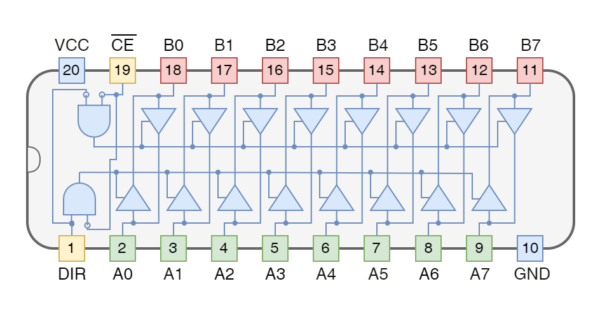

图 8:使用三态缓冲器的双向(收发器) 三态缓冲器的“启用”输入之一处的非门确保只有其中一个保持启用状态。在此配置中,“启用”输入用作方向/数据流控制输入。例如,当“Enable”设置为“HIGH”时,数据/信号从“A”流向“B”,否则(如果“Enable”设置为“LOW”),则从“B”流向“A” ”。因此,使用“启用”输入,数据/信号可以设置为沿任一方向流动,从而允许双向通信。双向缓冲器也可采用 IC 封装(如 TTL 74LS245 和 CMOS 74ALS620(反相))进行商业化购买,并可用作总线收发器。 总线收发器 总线收发器是一种基于三态缓冲器的设备,允许两条总线之间双向数据/信号或控制两个电路之间的双向通信。总线收发器用于面向总线的系统,以促进数据总线之间的受控和双向接口/通信。下图中显示了八 (8) 线收发器 TTL 74LS245 。

图 9:TTL 74LS245 八路收发器 该八进制三态缓冲器器件可用于连接 8 位数据总线,以实现双向和受控异步数据通信。使用“DIR”输入,可以设置数据流的方向。例如,当它设置为“HIGH”时,数据将从标记为“A”的端子流向标记为“B”的端子,并在“DIR”设置为“LOW”时反转方向。此外,芯片使能“CE”输入可启用或禁用三态缓冲器的功能。“CE”上的条表示它是反相逻辑输入,当设置为“LOW”时,“CE”将被视为启用。 结论 收发器是一种基于三态缓冲器的设备,它允许总线之间的双向(双向)通信或用作接口电路。三态缓冲器是缓冲器的一种形式,允许信号/数据通过而无需任何改变或决策。与只有两个端子和两个输出状态的传统缓冲器相比,三态缓冲器具有额外的“启用”输入,并具有第三种高阻抗 (High-Z) 状态。三态缓冲器具有三 (3) 个输出状态,即“高”、“低”或“高 Z”,具体取决于数据输入处的信号和“启用”输入的状态。处于“Hi-Z”状态的三态缓冲器表现为开路并隔离两个端子或输入和输出。此功能使它们适合与连接多个设备的单个/公共/共享数据总线进行通信。通过将两个三态缓冲器置于反向并行配置中并在“启用”输入之一使用非门,可以构建双向/收发器。在此配置中,“启用”输入充当方向控制输入。总线收发器基于双向三态缓冲器,用于面向总线的系统或接口电路。八进制三态双向缓冲器,例如 TTL 74LS245,可用于将 8 位设备与共享/公共数据总线连接。