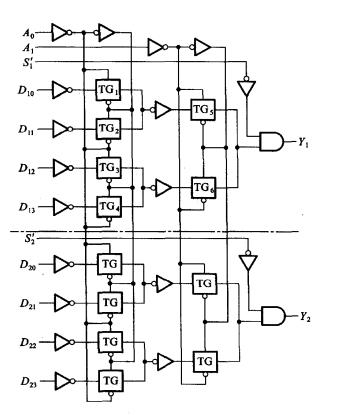

现以双 4 选 1 数据选择器74HC153 为例,说明它的工作原理。图4.3.21 是74HC153 的逻辑图,它包含两个完全相同的4选1数据选择器。两个数据选择器有公共的地址输入端,而数据输入端和输出端是各自独立的。通过给定不同的地址代码(即AA的状态),即可从4个输入数据中选出所要的一个,并送至输出端Y。图中的S′和S′是附加控制端,用于控制电路工作状态和扩展功能。

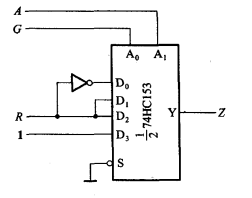

A将上式稍加变换即可化成与式(4.3.18)完全对应的形式GZ=R′(A′G′)+R(A′G)+R(AG′)+1(AG)A。A(4.3.20)DDsū芋将式(4.3.20)与式(4.3.18)对照一下便知,只要令数据选择器的输入为Y|zDR1D-|~A=AD=R′sA=G D=D=RD=1

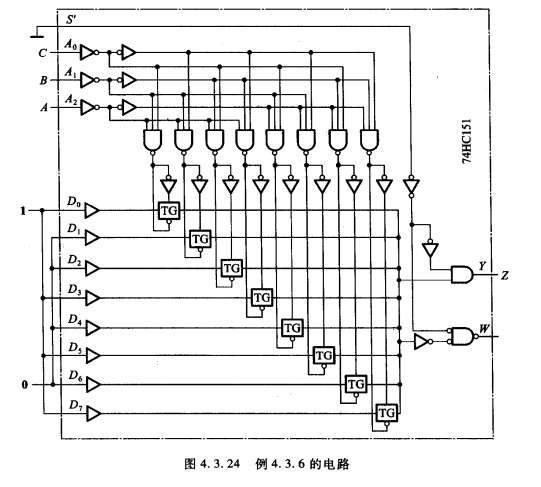

图4.3.23 例4.3.5的电路如图4.3.23 所示,则数据选择器的输出就是式(4.2.2)所要求的逻辑函数 Z。【例4.3.6】 试用8 选 1 数据选择器产生三变量逻辑函数Z=A′B′C′+AC+A′BC(4.3.21)解: 8 选 1 数据选择器

有3 位地址输入((n=3),能产生任何形式的四变量以下的逻辑函数,故定可生成式(4.3.21)的三变量逻辑函数。图4.3.24中虚线框内部分是8 选1 数据选择器74HC151 的逻辑图

在控制端输入S′=0(S=1)的情况下,输出的逻辑式为(4.3.22)将式(4.3.21)化成与式(4.3.22)中 Y 对应的形式得到Z=A′B′C′+AC+A′BC=1(A′B′C′)+0(A′B′C)+0(A′BC′)+1(A′BC)+0(AB′C′)+1(AB′C)+0(ABC′)+1(ABC)(4.3.2,).

将以上两式对照一下可知,只要令数据选择器的输入为A=AA=B D=D=D=D=1A=C

D=D=D=D=0则数据选择器的输出Y 就是所需要的逻辑函数Z。电路的接法如图4.3.24所示。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。