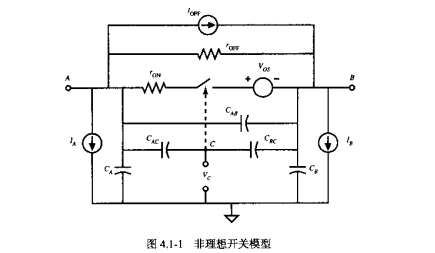

开关在集成电路设计中有很多作用。在模拟电路中,开关被用来实现诸如电阻的开关仿真[1]等有用的功能,开关同样也用于多路选择、调制和其他许多应用。在数字电路中,开关被用做传输门,并加入了在标准逻辑电路没有的尺寸的灵活性。本节的目的是研究与CMOS集成电路兼容的开关特性。我们从电压控制开关的特性开始。图4.1-1 所示为该器件模型。电压vc控制开关的状态——开或关。

电压控制开关是一个三端网络,其中A、B端组成开关, C端是控制电压vc作用端。开关重要的特性是它的导通电阻 row和关断电阻rorr。理想情况下, roN为零而rom,为无穷大,实际上并非如此。此外,这些值与端口条件有关, 绝不会是常数。通常,开关会有一些电压偏移,图4.1-1中用V模拟。V表示当开关为导通状态、电流等于零时,端点A和B之间存在的小幅值电压。IorF表示开关为断开状态的漏电流。电流.、lA、lB表示开关端点与地之间的漏电流(或其他电源电压)。图4.1-1中偏移源和漏电流的极性是不确定的,图中的方向是任意标注的。在模拟采样数据电路应用中,寄生电容是一个需认真考虑的问题。电容(CA和Cb是开关端A、B与地之间的寄生电容。电容CAB是开关端A、B之间的寄生电容。电容(CAc和C,C是存在于电压控制端C和开关端A、B之间的寄生电容。电容CAc和C的影响称为电荷馈通——由此控制电压的一部分会出现在开关A、B端。

式(4.1?2)中的Q是晶体管的静态工作点。图4.1-3说明了 n沟道管漏极电流随漏、源电压变化的曲线,其中管子的宽长比W/L=5/1,vas等间隔增加。此图说明了 MOS管工作的一些重要原理。注意, 图中的曲线并不是关于V=0对称的。这是因为晶体管端(漏、源)开关起着V过零的转换作用。例如,当V为正时, B点是漏极, A 点为源极, 且V固定为2.5V,VCs由给定的v固定。当V为负时, B点为源极, A 点为漏极, 且V和VBS连续减少, 而VCS增加,从而导致电流增加。v=5v3.5/V=4Vv3.025vc=3V2.5vc=2vν20vc=1V171.50.50.0-0.510250.025V(V)图4.1-3 n沟道管用做开关的I-V特性

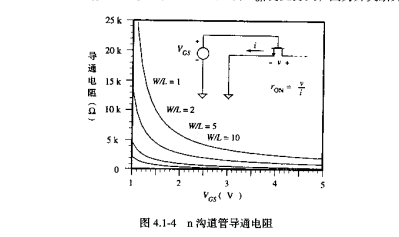

图4.1-4显示了当VD5=0.1V,W/L=1,2,45 和10时 roN随VOS变化的图.从图中可以看出W/L越大, row越低。 当Vcs减到VT(Vr=0.7V)时,roN为无穷大,因为开关断开。25kiyc20kw>115krom<17导通电阻CM=210kW/L=5ML=105k023145.Vcs(V)图4.1-4 n沟道管导通电阻 当V小于或等于V时, 开关断开,理想情况下 roFF为无穷大。当然,它不可能为无穷大。

但因为它非常大,截止状态的性能由漏极-体和源极-体的漏电流决定,就像亚阈值电压区从漏到源的漏电流一样。从源和漏到体的漏电流主要是 pn结漏电流,在图4.1-1 中用lA和l模拟。

免责声明: 凡注明来源本网的所有作品,均为本网合法拥有版权或有权使用的作品,欢迎转载,注明出处。非本网作品均来自互联网,转载目的在于传递更多信息,并不代表本网赞同其观点和对其真实性负责。