如果说探索外太空是人类的浪漫,那么为各类航天器,飞行器设计IC芯片,就是工程师的浪漫,而芯片作为重要的宇航级器件之一承担了重要使命。

2021年12月,北斗三号系统卫星总设计师林宝军出席公开活动时表示,北斗三号卫星目前器件包括国产龙芯CPU、国产FPGA、国产ASIC、载荷的微波器件等全部实现自主可控。

林宝军自2011年起任北斗三号卫星总设计师,全面主持了导航卫星研制工作,带领团队攻克了数十项关键技术。

北斗三号卫星的“心脏”使用国产龙芯CPU(龙芯3A抗辐照型),同时还用上了国产FPGA、ASIC和微波器件等,器件实现100%自主可控,彻底扭转卫星关键部件依赖进口受制于人的局面。

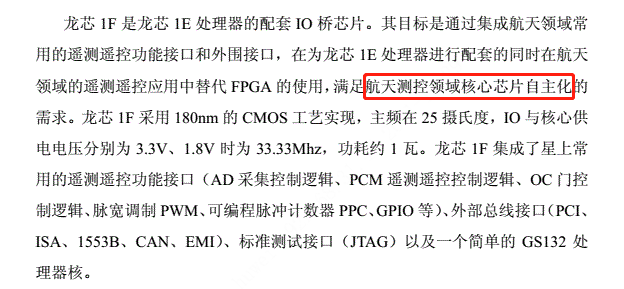

据了解,截至2020年,就有10颗北斗导航卫星搭载了龙芯3号CPU,同时进入卫星的还有国产Flash和功率放大器等器件。早在2015年,就首次在卫星上使用了龙芯CPU,而且一用就是两款:龙芯1E和龙芯1F抗辐照处理器。当时龙芯1E和龙芯1F的售价仅为几万元一片,而西方愿意出售给中国的宇航级芯片中,例如性能为100MIPS的美国ATMEL AT697F要20万到30万元一片,性能更好的赛灵思XQR5VFX130-CF1752价格高达上百万元一片。

据北斗卫星研发人员介绍,新一代北斗卫星上有3个被称为“单机”的黑盒子,每个约有4本400页的32开图书摞起来那么大。其中两个黑盒子里,每个装了2片龙芯1E芯片和4片龙芯1F芯片。

龙芯1E负责进行常规运算,龙芯1F完成数据采集、开关控制、通讯等处理功能。龙芯1家族采用180nm CMOS工艺、400万晶体管。虽然性能上与先进水平还有较大的差距,但是可靠性方面不相上下。关键的是,龙芯1E/1F的出现使国产CPU首次具备了较强的抗辐照能力。

北京时间2022年2月9日(美国东部时间2月8日),SpaceX(美国太空探索技术公司)表示,该公司于2月3日发射的一批49颗星链卫星,有40颗因受地磁暴影响而已经或将要在大气层坠毁。

根据SpaceX说法,这批卫星发射后的第二天,就受到地磁暴影响,导致卫星所在区域的大气温度上升、密度增加。星载GPS显示,卫星受到的大气阻力较发射前增加了50%,许多卫星很快因大气阻力而脱离轨道。

其实,包括卫星、航天飞机、空间站等在内,游弋在太空中的各种人造飞行器,其内部都含有各类芯片、器件、板卡等大量电子设备。目前,在地球环境内所使用的电子器件等产品。

刚刚在圣诞节发射的詹姆斯韦伯太空望远镜搭载的就是一颗主频为118MHz的RAD750芯片,这颗CPU于2001年发布,工艺仅为150nm,TDP仅为5W。这颗CPU只有上世纪的孱弱性能,但能承受2,000-10,000戈瑞(Gy.)的辐射,大约是做CT的1千万倍,也是单颗售价约29万美元的卖点。

而韦伯的大表哥——哈勃望远镜,至今仍然运行在英特尔的80486上。

同时,RAD750还运行在毅力号火星车和100多颗卫星上,接受宇宙“考验”近二十年目前无一故障。

这些奇奇怪怪的宇航级CPU性能和消费级产品完全不在一个时代,同时指标根据任务需求高度定制化。

那制造一颗航天级的芯片有多难?

1.宇航级芯片所处的空间环境

在航天器运行的空间环境中,存在着大量的高能粒子和宇宙射线。这些粒子和射线会穿透航天器屏蔽层,与元器件的材料相互作用产生辐射效应,引起器件性能退化或功能异常,影响航天器的在轨安全。引起器件辐射效应的主要空间辐射源包括地球辐射带、银河宇宙射线、太阳宇宙线和人工辐射。

其中,对芯片工作影响为严重的辐射效应当属“单粒子效应”。

据数据统计,从 1971 年到 1986 年间,国外发射的 39 颗同步卫星共发生了 1589 次故障,有 1129 次故障与空间辐射有关,且其中的 621 次故障是由于单粒子效应导致的。这些统计数据说明了航天应用中电子器件的主要故障来自于空间辐射,而单粒子效应导致的故障在其中占较大比重。

这些故障中,部分是性不可逆的,如发生单粒子锁定导致芯片内部局部短路从而产生大电流烧毁器件。针对此类错误可以应用一些特定工艺或器件库来避免。而太空中大部分错误是由于半导体器件的逻辑状态跳变而导致的可恢复的错误,如单粒子翻转导致存储器存储内容错误。

单粒子翻转(Single-Event Upsets,SEU)指的是元器件受辐照影响引起电位状态的跳变,“0”变成“1”,或者“1”变成“0”,但一般不会造成器件的物理性损伤。正因为“单粒子翻转”频繁出现,因此在芯片设计阶段需要重点关注。这也是这篇文章的重点。

2.在芯片设计阶段如何防护“单粒子翻转”

(1) 选择合适的工艺制程

在航天领域,并不是工艺制程越小越好。通常来讲,工艺制程越小,抗辐照能力越差。因此,为了确保可靠性,一般会选择较大线宽的制程,比如0.18um、90nm、65nm等,而不会一味追求摩尔定律的前沿制程。

(2)加固标准单元工艺库

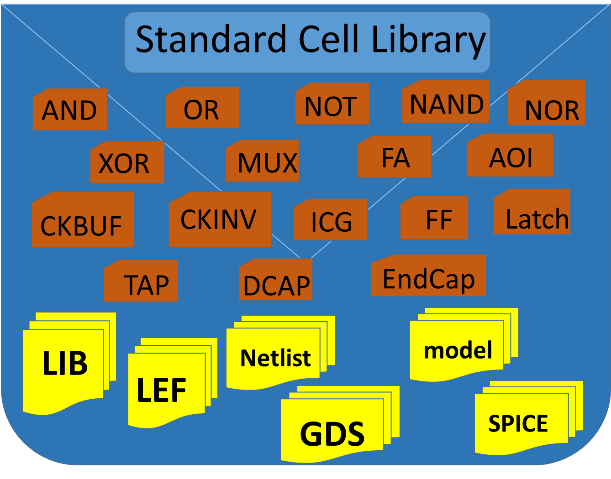

标准单元工艺库是数字芯片的基石。如果把数字芯片看做一个建筑,标准单元工艺库就是构成建筑的砖块。标准单元工艺库包括反相器、与门、寄存器、选择器、全加器等多种基本单元,每一个标准单元对应着多个不同尺寸(W/L)、不同驱动能力的单元电路,基于这些基本单元即可构成复杂的数字芯片。

鉴于数字芯片的超大规模,已经很难通过全定制电路结构的方式来设计,而直接对商用工艺库进行加固则是设计成本的选择。在制造厂商提供的标准单元库基础上结合抗辐照加固措施,使设计出来的输入输出单元库具有抗辐照能力。加固之后的工艺库需要晶圆厂流片验证。

(3)设计冗余化

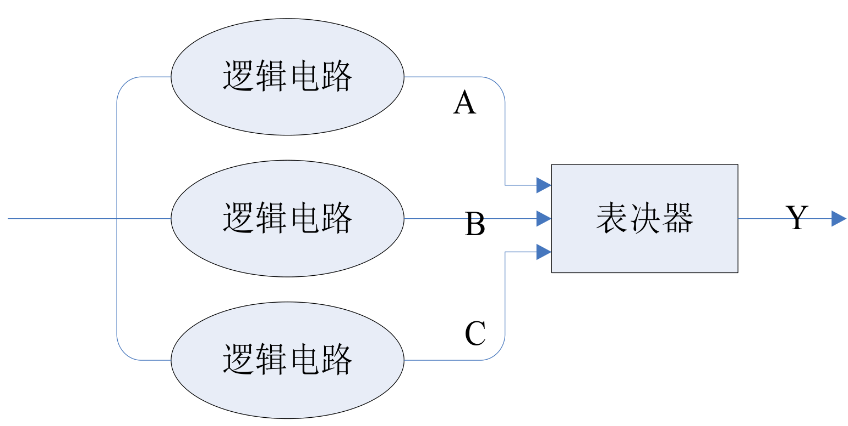

在抗辐照加固方法中,三模冗余(TMR)是有代表的容错机制。同一时间三个功能相同的模块分别执行一样的操作,鉴于单粒子翻转瞬时仅能打翻1路,“三选二”的投票器将会选出其余两路的正确结果,增强电路系统的可靠性。三模冗余显著优点是纠错能力强,且设计简单,大大提高电路可靠性;但缺点也是显而易见,会将电路增大3倍以上。TMR的方法较为灵活,可根据性能需求在寄存器级、电路级、模块级等任意层次设计TMR,部分EDA工具也可自动插入。

结尾

虽然上述方法可以很好地防护单粒子翻转效应,但是也给逻辑综合、布局布线带来很多困扰,在芯片物理实现过程中需要小心谨慎应对。除上述方法外,还可引入Muller C单元、双互锁存储单元结构(DICE)对晶体管级电路进行防护,也可在版图阶段使用环形栅替换条形栅。