信号特征的描述

信号完整性研究的是如何使驱动器输出的信号传输到接收器件并被正确接收。由此,我们定义了信号完整性的三要素分别是:

对一个信号进行描述通常需要如下几个指标:

信号特性的描述

** 摆幅:** 信号从低电平到高电平之间的电压差,对于单端信号通常由信号的供电电压决定。通常情况下摆幅越大越不容易出现信号完整性问题,但随着半导体工艺的进步信号的摆幅在不断地降低。就拿存储器来说早期的SDRAM还是3.3V的TTL电平,而DDR3采用SSTL电平电压已经达到了1.35V,现在即将量产的DDR5摆幅只有1.2V,LPDDR5的VDDQ电压甚至低到了0.5V。可想而知信号完整性面临的挑战越来越大。

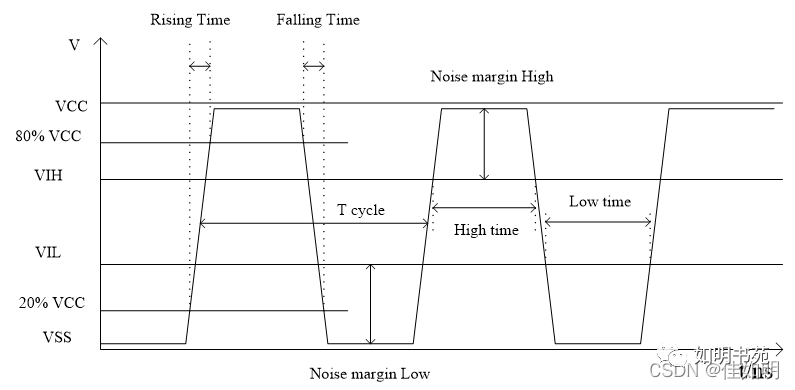

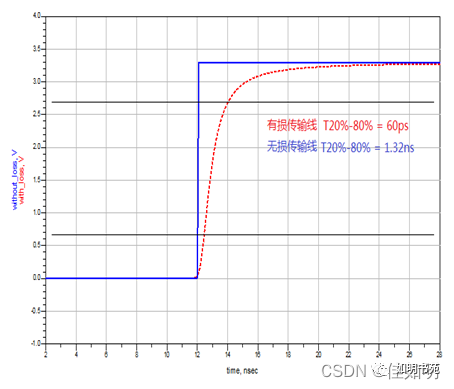

** 上升、下降时间:** 通常数据手册或者IBIS模型中都会定义信号从20% VCC到80% VCC(或者10% VCC到90% VCC)的时间。信号的上升下降时间决定了信号的带宽也就是信号的频域特性,信号的上升下降时间越小,信号的带宽越高,也就越容易产生信号完整性问题。通常情况下信号的上升下降时间受到芯片工艺、工作环境温度、供电电压等因素影响。

** 时钟频率:** 对于时钟信号波形重复出现的频率就是时钟频率,单位为Hz。时钟频率是时钟周期的倒数。通常情况下时钟频率越高,留给总线的时序裕量就越小,时序问题也就越突出。

** 数据速率:** 对于数据信号由于波形不像时钟那样周期性重复,衡量数据传输快慢不能单看时钟频率。数据速率的单位为bps(bit/s),即每秒传输的数据bit数。对于时钟单沿(通常为上升沿)采样的系统,数据速率在数值上等于时钟频率;而对于双沿采样的系统,数据速率在数值上等于时钟频率的两倍(如DDR的DQ信号)。

** 有效位宽:** 有效位宽分为高电平有效位宽和低电平有效位宽,是指信号保证为高或低电平的有效时间。在进行时序分析时必须保证接收端信号有足够的高低电平有效位宽来满足接收端对建立保持时间的要求。

** 噪声裕量:** 分为高电平噪声裕量和低电平噪声裕量,指的是信号高电平和低电平到高低电平判决门限VIH和VIL之间的电压差。噪声裕量越大数据传输的稳定性越好,如果噪声裕量为0或者负值,就会发生数据接收错误。

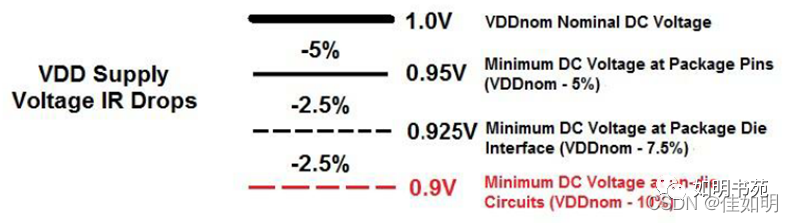

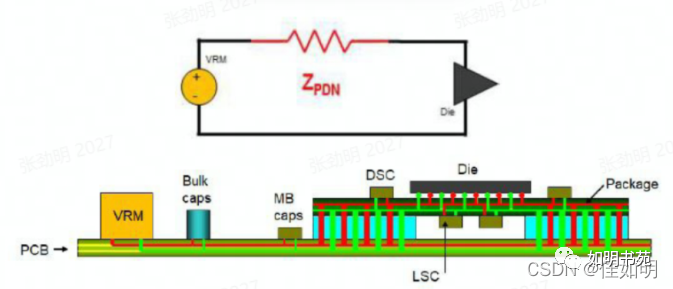

此外,我们也可以把 电源理解为一种特殊的信号 。芯片正常工作通常对PDN(电源传输网络)提出了要求即需要PDN在多长时间内提供多大的电流。同时芯片对芯片内部电路、封装、PCB级的电源波动都有明确要求。通常芯片内部电路允许的电源波动范围是?10% (具体还要看芯片的spec),而对于PCB板级设计来说器件管脚处的噪声要控制在?5%以内,此时我们就需要根据芯片电流的需求以及电压噪声的控制要求来设计整个PDN网络。

芯片对电流的需求

那么什么是信号完整性的破坏呢?

信号通过互连线由驱动端向接收端传输,由于阻抗匹配、布线拓扑、电源噪声、串扰等各种因素都会导致信号完整性问题。如果不能妥善解决信号完整性问题,那么在接收端接收到的信号波形就会发生畸变,产生的后果可能使总线不能满足系统时序需求、接收端接收到错误的数据或者击穿接收器件的Buffer对系统工作的稳定性造成影响,等等这些现象都叫作信号完整性破坏。

常见的信号完整性破坏包括以下几个方面:

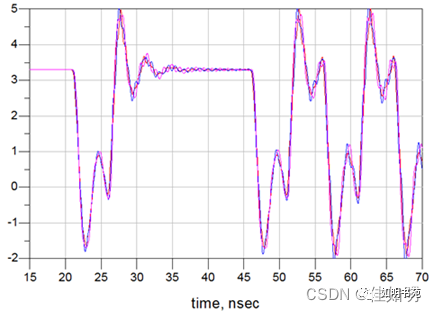

** 过冲(overshoot)和下冲(undershoot)** :过冲指的是信号超出供电电压VCC的电压或者低于参考地电压VSS的电压。当驱动器的驱动能力很强在源端和末端又没有良好的阻抗匹配时就会在接收端波形产生严重的过冲和下冲。过冲和下冲并不会对功能产生影响,但是长期工作在过冲条件下可能会导致芯片输入buffer击穿,从而影响器件的使用寿命。因此,一般的器件手册都会对过冲做出要求,有的器件会给出芯片所能承受的过冲电压,有的手册则是给出了对过冲面积(信号高于VCC或低于VSS部分的面积)的要求。

信号的过冲

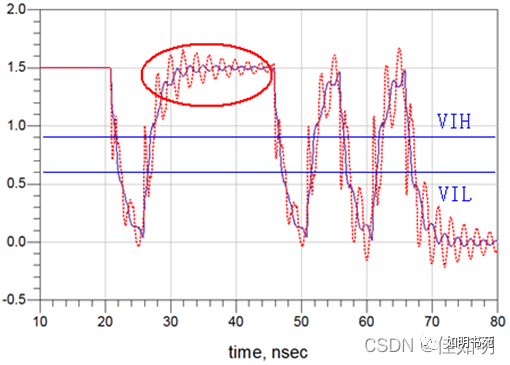

振铃(Ringback) :指接收端信号波形跳变之后并没有达到稳定电平而是产生向着门限电压“振荡”的电压波形。振铃的形成一般都是由于阻抗不连续导致多次反射产生,振铃使信号的噪声裕量减小,严重的振铃会导致接收错误。此外,振铃还会导致信号高频能量变多从而增大EMI问题,因此必须对其加以控制。

信号高低电平存在的振铃

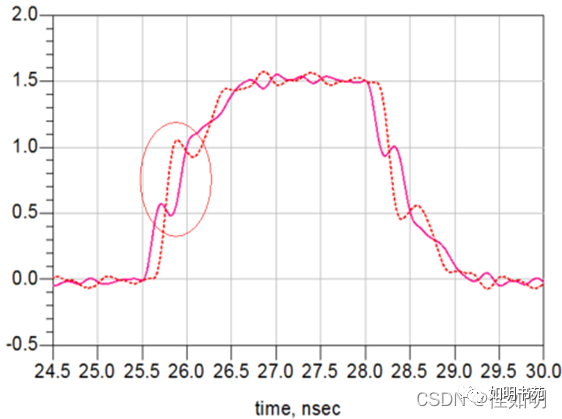

** 边沿不单调:** 指的是信号上升沿或者下降沿存在回沟的现象。由于阻抗突变、串扰等互连线中的非理想效应有可能导致信号的上升下降边沿出现台阶或者回沟。对于时钟信号通常要求有单调的上升/下降边沿用以对数据信号进行采样;对于数据信号如果存在回沟也会使数据信号的有效位宽减小,从而减小时序裕量。

信号边沿不单调

** 边沿退化:** 指的是驱动器输出的信号经过传输线传输后信号的边沿相对于驱动器输出信号边沿会明显变缓的现象。边沿退化的原因可能是传输线的损耗或者负载的电容效应、其它信号的干扰、同步开关噪声以及驱动器驱动能力不足等等。边沿退化的影响主要体现在一些器件可能对信号上升下降时间做出了要求(如时钟等),不能达到上升下降时间将导致无法触发器件执行正确的操作;也可能导致数据信号上升下降时间的。

信号的边沿退化

** 信号之间的偏移(skew** ) :接收端接收到的一组信号之间的时间差。主要由于信号的传输路径上的延时不同、驱动器本身的输出skew、以及信号传输过程中所遇到的噪声干扰、同步开关噪声等因素的影响造成。驱动器本身的输出skew我们无法控制,只能作为设计的约束条件。我们要做的就是控制信号传输路径上的上的延时以及一切对传输延时有影响的负面因素。一般在做DDR等高速并行总线设计时需要严格控制同组数据之间的skew来达到时序裕量化。

** 抖动(jitter** ) :指的是信号边沿与其理想位置的偏差。在进行高速并行总线设计时过大的抖动会导致时域裕量的减小,在做高速串行总线设计时过大的抖动会导致误码率不达标。抖动的来源有很多包括电源噪声、PCB布线、串扰、环境温度、EMI辐射等等。

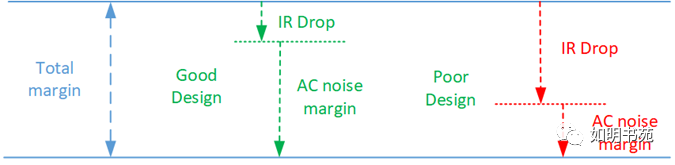

** 电源完整性**在高速信号传输过程中有着非常重要的作用。互连线路通流不足导致电压降太大、电源网络的滤波设计不好导致电源噪声超标,等等这些现象都叫作电源完整性破坏。接口电源完成性的破坏会直接导致相应接口信号的噪声、时序裕量的降低;内核电源完成性的破坏会直接导致处理器内部的指令无法正确传输。由此可见,电源完整性设计的目的就是保障用电芯片有稳定的电源供应,保证芯片正常工作。

如果把电路板比作人体,那么电流则是电路板的血液,电源则是心脏完成向大脑和四肢躯干(芯片)供血的工作。可想而知电路板上由电源到芯片的供电通路,也就是PDN网络的作用有多重要了。

人体的血液流通不畅,可能导致脑梗、心梗,而电路板的PDN设计不好,也可能导致整个系统的瘫痪。电源完整性的指标分为AC和DC两个部分,但AC和DC之间并不相互独立,而是共同决定电源的性能。

如果这些问题单一的出现分析和解决并不会很麻烦,我们在实际设计中面临的情况是非常复杂的可能会有很多因素作用在一起共同导致信号质量的恶化。此时就需要我们掌握信号完整性分析的手段找到产生问题的原因,并进行有针对性的整改、优化使其满足设计要求。